Date: December 11, 2007 Student name:

# **General requirements for the exam:**

- 1. This is CLOSED BOOK examination;

- 2. No questions allowed within examination period;

- 3. If something is not clear in question please, put your assumptions;

- 4. No extra papers cell-phones or programmable calculators are allowed;

- 5. For calculations or assumptions you can use reserved space in the exam paper or opposite side of each page;

- 6. **It is allowed for use**: Pens and pencils, erasers, simple calculators and rulers.

- 7. All explanations in boxes and tables has to be printed

# **Section:** Synthesis of Application Specific Computing Architecture

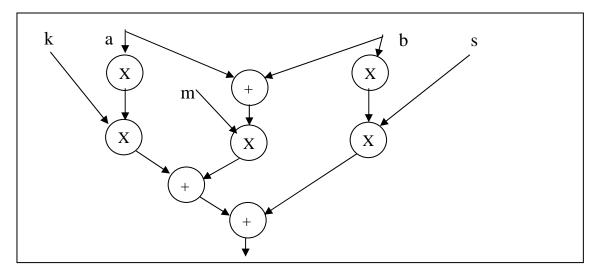

Create the architecture for the application specific data-path for vector processing using the following function:  $\mathbf{y} = k^*a^2 + s^*b^2 + m^*(a+b)$

The data segment consists of two vectors, where each vector can contain 32, 64, 128 or 256 elements:  $A = [a_1, a_2, a_3...a_n]$  and  $B = [b_1, b_2, b_3...b_n]$ , where n = 32, 64, 128, 256. Each pair of elements of the above vectors:  $a_i$  and  $b_i$  for i=1, 2, 3, ...n has to be processed by the given formula during the same execution cycle. Coefficients -k, s, and m are scalar (integer) data, which stay constant during the period of entire vector processing.

### Question 1.1 (5 marks)

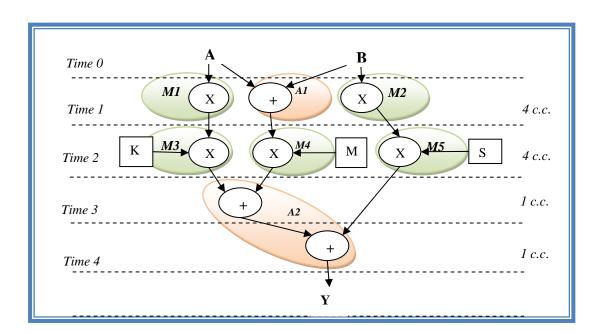

In the Box below (Figure 1.1) draw the sequencing graph scheduled with assumption that there is no limit for any logic resources (maximum possible resources can be used and each operation can start "as soon as possible".

**Figure 1.1:** Sequencing Graph with unconstraint scheduled (ASAP algorithm)

### Question 1.2 (5 marks)

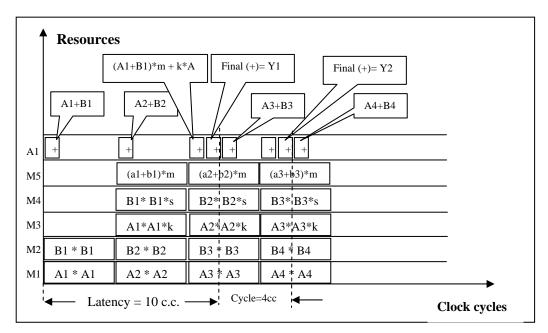

a) Calculate the maximum number of adders and multipliers for the case of fully pipelined data-path:

Number of adders = 1 Number of multipliers = 5

- b) Calculate latency and cycle time (in case of fully pipelined data path) when:

- i) "Adder" requires 1 clock cycle (c.c.) for the operation and

- ii) "Multiplier" takes 4 c.c. for multiplication.

Latency =  $\underline{10}$  c.c. Cycle time =  $\underline{4}$  c.c.

Please provide time schedule in Figure 1.2 (below) according to sequencing graph in Figure 1.1. This schedule should reflect moment of start and finish of each operation for each of resources (adder- A1, A2, etc. and multipliers – M1, M2, etc.) during the time slots.

Figure 1.2: Schedule of resource usage for the first cycle (Latency) and further cycles

### Question 1.3 (5 marks)

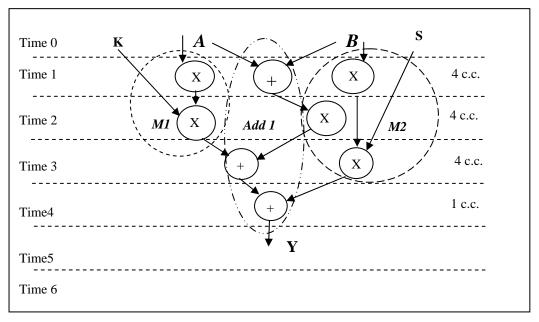

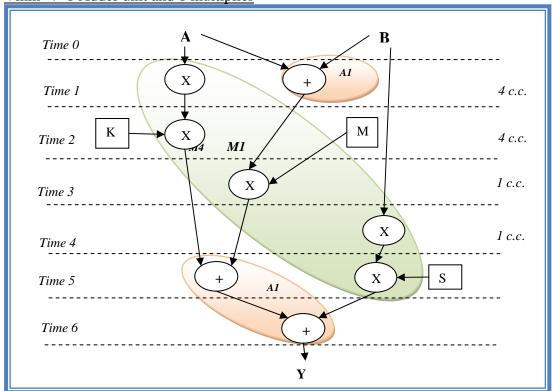

In the Box below (Figure 1.3) draw the sequencing graph scheduled with assumption that there are two multipliers and one adder available for this function and each operation can start "as soon as possible".

Figure 1.3: Binded sequencing graph scheduled by ASAP algorithm

### **Question 1.4 (5 marks)**

Calculate latency and cycle time for this data path (Figure 1.3) when:

- i) "Adder" requires 1 clock cycle (c.c.) for the operation and

- ii) "Multiplier" takes 4 c.c. for multiplication.

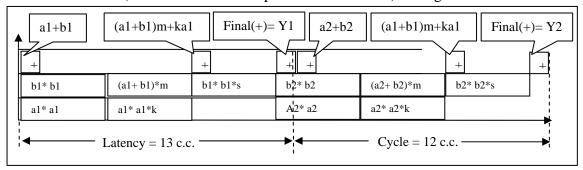

Latency =  $\underline{13}$  c.c. Cycle time =  $\underline{12}$  c.c.

Please provide time schedule in Figure 1.4 (below) according to sequencing graph in Figure 1.3. This schedule should reflect moment of start and finish of each operation for each of resources (adder- "A" and multipliers – M1 and M2) during the time slots.

Figure 1.4: Schedule of resource usage for the first cycle (Latency) and further cycles

## **Question 1.5 (5 marks)**

Conduct the procedure for conversion of the sequencing graph scheduled and binded according to resource constraints described in Question 1.2.

a) Fill the Table 1.1 for the Component "Adder" according to resource constraints and scheduled time slots.

Table 1.1

| Time Slot | Operation | Input 1   | Input 2   | Output   |

|-----------|-----------|-----------|-----------|----------|

| 0         | NOP       | A         | В         | -        |

| 1         | +         | -         | -         | M2 input |

| 2         | NOP       | M1 output | M2 output | -        |

| 3         | +         | A1 output | M2 output | A1input  |

| 4         | +         | A         | В         | Y        |

| 5         |           |           |           |          |

b) How many sources have to multiplex each of input MUX (Multiplexers) and how many outputs have to de-multiplex DeMUX of the "Adder" Component (see Table 1.1)

Number of inputs for: a) Input 1 MUX = 3; b) Input 2 MUX = 2

Number of DeMUX outputs =  $\underline{\phantom{a}}$

# 2 Section: Optimization of Application Specific Computing Architecture

Find the optimal architecture of Application Specific Processor (ASP) for the above function:  $\mathbf{y} = k^* a^2 + s^* b^2 + m^* (a+b)$  and data structure which consists of two vectors, where each vector can contain 32, 64, 128 or 256 elements:  $\mathbf{A} = [a_1, a_2, a_3...a_n]$  and  $\mathbf{B} = [b_1, b_2, b_3...b_n]$ , where n = 32, 64, 128, 256. Each pair of elements of the above vectors:  $\mathbf{a}_i$  and  $\mathbf{b}_i$  for i = 1, 2, 3,...n has to be processed by the given formula during the same execution cycle. Coefficients -k, s, and m are scalar (integer) data, which stay constant during the period of entire vector processing.

The optimization requirements are as follows: ASP should process vectors **A** and **B** with 256 elements in each not longer than 3080 clock cycles taking minimum area units.. The resources available are as follows:

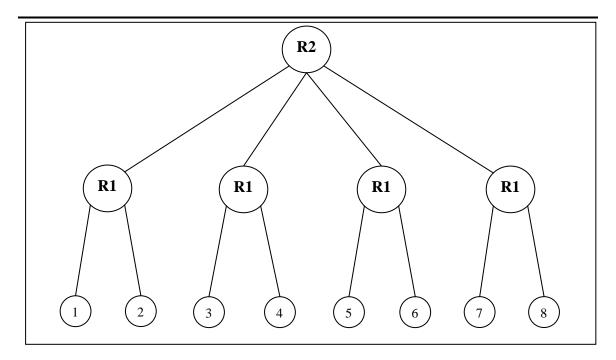

**R1:** "Adder" may be used in variants: R1.1 – one adder unit or R1.2 – two units in ASP **R2:** "Multiplier" may be used as: R2.1 – one multiplier, R2.2 – two multipliers, R2.3 – four multipliers and R2.4 – five multipliers in ASP

### Resource specification:

The period of "ADD" operation = 1 clock cycles

The period of "MULT" operation = 4 clock cycles

One Adder unit requires 20 area units (au) on the chip (e.g. 20 CLBs in the FPGA)

One Multiplier unit requires 100 area units (au)

### Question 2.1 (20 marks)

Provide the Mini-Max analysis of ASP architecture for the above task

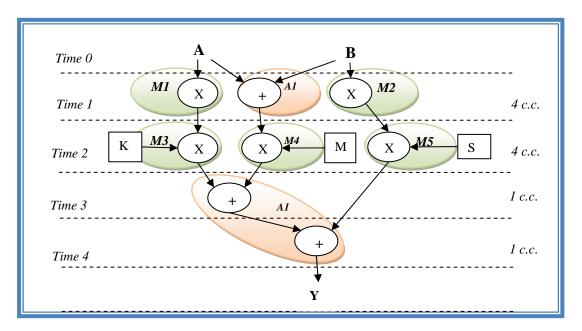

**Q2.1.1:** In the box below present the scheduled sequencing graph with resource binding for the variant of architecture which employs maximum of computation resources – Vmax => 2 Adders units and 5 multipliers

**Q2.1.2:** Calculate the latency of execution of first pair of vector elements:  $a_1$  and  $b_2$  and cycle time for the rest of vector elements (in clock cycles):

Latency (V max) =  $\underline{10}$  c.c.

Cycle time (V max) =  $\underline{4}$  c.c.

**Q2.1.3**: Calculate total execution time of full data vectors (256 elements of a and b)

Total execution time  $(Vmax) = \underline{1030}$  c.c.

Show calculations here T exe (Vmax) = Latency + (N-1) x Cycle time =  $= 10 \text{ c.c.} + (256-1) \times 4 \text{ c.c.} = 1030 \text{ c.c.}$

**Q2.1.4:** Calculate total area to be used for the V max

Total area =  $\underline{5}$  (Multipliers) x 100 au + 2 (Adders) x 20 au =  $\underline{540}$  au

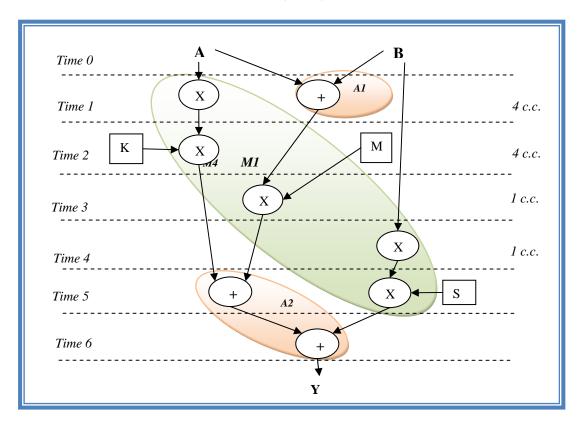

**Q2.1.5:** In the box below present the scheduled sequencing graph with resource binding for the variant of architecture which employs minimum of computation resources – Vmin => 1 Adder unit and 1 multiplier

Q2.1.6: Calculate the latency of execution of first pair of vector elements:  $a_1$  and  $b_2$  and cycle time for the rest of vector elements (in clock cycles):

Latency (V min) = \_\_21\_\_\_ c.c.

Cycle time (V min) =  $\underline{20}$  c.c.

<u>Q2.1.7</u>: Calculate total execution time of Total execution time (Vmin) =  $\underline{5121}$  c.c.

Show calculations here

Texe (V min) = Latency + (N-1) x Cycle time = 21 c.c. + 255 x 20 = 5121 c.c.

Q2.1.8: Calculate total area to be used for the V min

Total area =  $\underline{1 \times 20 \text{ au} + 1 \times 100 \text{ au}} = \underline{120} \text{ au}$

### Question 2.2 (25 marks)

Conduct the analysis of Critical variants of ASP architecture for each of resources: R1 – "Adder" and R2 – "Multiplier"

**Q2.2.1:** Identify the critical variant of ASP for the "Adder" (R1): put number of units for the each resources in variant identification below (near "?")

## Vcr (R1) => 1 Adder units and 5 Multipliers

In the box below present the scheduled sequencing graph with resource binding for the critical variant of architecture for the R1 (adder)

Q2.2.2: Calculate the latency of execution of first pair of vector elements:  $a_1$  and  $b_2$  and cycle time for the rest of vector elements (in clock cycles):

Latency ( $V \operatorname{cr}[R1]$ ) =  $_10_{-10}$  c.c.

Cycle time  $(V \operatorname{cr}[R1]) = \underline{4} \operatorname{c.c.}$

**Q2.2.3:** Calculate total execution time of full data vectors (256 elements of a and b)

Total execution time  $V \operatorname{cr}[R1] = \underline{1030} \operatorname{c.c.}$

Show calculations here

T exe (Vmax) = Latency + (N-1) x Cycle time = 10 c.c. + (256-1) x 4 c.c. = 1030 c.c.

**Q2.2.4:** Identify the critical variant of ASP for the "Multiplier" (R2): put number of units for the each of resources in variant identification below (near "?")

# Vcr (R2) => 2 Adder units and 1 Multipliers

In the box below present the scheduled sequencing graph with resource binding for the critical variant of architecture for the R1 (adder)

**Q2.2.5**: Calculate the latency of execution of first pair of vector elements:  $a_i$  and  $b_i$  and cycle time for the rest of vector elements (in clock cycles):

Latency (V cr[R2]) =  $\underline{21}$  c.c.

Cycle time  $(V \operatorname{cr}[R2]) = \underline{20} \operatorname{c.c.}$

**Q2.2.6:** Calculate total execution time of full data vectors (256 elements of a and b)

Total execution time  $V \operatorname{cr}[R2] = \underline{5121} \operatorname{c.c.}$

Show calculations here

Texe (V min) = Latency + (N-1) x Cycle time = 21 c.c. + 255 x 20 = 5121 c.c.

Page

## Question 2.3 (15 marks)

Conduct the partial arrangement of Architecture Configurations Graph (ACG) representing the design space for the above ASP in order of:

- i) Decrease the total execution time from the left terminal to the right terminal of ACG;

- ii) Increase the area utilized for resources from time from the left terminal to the right terminal of ACG. Note: The hierarchical arrangement criterion:

K(Ri) = [Total exec. Time for Vcr(Ri) - Total exec. Time for Vmax] / (mi - 1), where  $m_i$  – number of variants of the resource Ri

**Q 2.3.1:** Calculate arrangement criterion for "Adder" – R1

$$K(R1) = \underline{(1030 - 1030) / (2-1)} = \underline{\mathbf{0}}$$

**Q 2.3.2:** Calculate arrangement criterion for "Multiplier" – R2

$$K(R2) = _{(5121-1030)/(4-1)} = 1707$$

**Q 2.3.3:** In the box below present the partially arranged ACG with identification of all nodes and edges (e.g. Root  $\rightarrow Ri$ , edge - Ri, etc.)

Figure 2.1: Partially arranged ACG

**Question 2.4 (15 marks)** Select the optimal variant of ASP architecture for the given function which must: i) provide the computation of full vectors during the period not exceeding 3080 c.c. and ii) with minimum possible resources (area units)

Note: The arrangement of ACG by area utilized for resources is in opposite to arrangement of ACG by total execution time (e.g. variant which provides shorter execution time may require more area units – see Figure 2.1).

**Q 2.4.1:** Provide the binary search procedure checking variants # 4 and #6 or #2, etc. to find the border variant number = terminal # on ACG in Figure 2.1. Point the border variant by \*- mark.

Optimal variant number is \_V#\_3\_ - One Adder and two Multipliers

Total execution time for  $V#4 = _3073$ \_\_\_ < 3080 c.c. ? Yes / No

Total execution time for  $V\#\underline{2} = \underline{5121} \leq 3080 \text{ c.c.}$ ? Yes /  $\underline{No}$

Total execution time for  $V#\underline{3} = \underline{3073} \le 3080 \text{ c.c.}$ ? Yes / No

$\underline{\mathbf{O}}$  2.4.2: Calculate the Total execution time for the optimal variant working with clock frequency = 100 MHz

Total execution time (ASPopt) = \_\_\_\_\_30.73\_\_\_ uS (micro-seconds)

Show calculations here

Texe = 3073 c.c. x 1 / 100 x 10  $^6$  = 30.73 micro sec.

**Q2.4.3:** Calculate total area to be used for the Vopt = V3

Total area (minimum) for Varian #  $3 = 1 \times 20$  au +  $2 \times 100$  au = **220 au**