# **Avalon Bus Specification**

## **Reference Manual**

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Document Version: 2.3 Document Date: July 2003

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents

and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

This manual provides comprehensive information about the Altera  $^{\textcircled{R}}$  Avalon  $^{\texttt{TM}}$  Bus.

Table 1 shows the reference manual revision history.

| Table 1. Reference Manual Revision History |                                                                                                         |  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------|--|

| Date                                       | Description                                                                                             |  |

| July 2003                                  | Corrected timing diagrams.                                                                              |  |

| May 2003                                   | Minor edits and additions.                                                                              |  |

| January 2003                               | Revised the "Avalon Read Transfer with Latency" and "Avalon<br>Interface to Off-Chip Devices" sections. |  |

| July 2002                                  | Minor edits and additions. Replaced Excalibur logo on cover with Altera logo - version 1.2              |  |

| April 2002                                 | Updated PDF - version 1.1                                                                               |  |

| January 2002                               | Initial PDF - version 1.0                                                                               |  |

### How to Find Information

- The Adobe Acrobat Find feature allows you to search the contents of a PDF file. Click the binoculars toolbar icon to open the Find dialog box.

- Bookmarks serve as an additional table of contents.

- Thumbnail icons, which provide miniature previews of each page, provide a link to the pages.

- Numerous links, shown in green text, allow you to jump to related information.

### How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at http://www.altera.com.

For technical support on this product, go to http://www.altera.com/mysupport. For additional information about Altera products, consult the sources shown in Table 2.

| Table 2. How to Contact Altera |                                                                   |                                                                       |  |  |

|--------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Information Type               | USA & Canada                                                      | All Other Locations                                                   |  |  |

| Technical support              | http://www.altera.com/mysupport/                                  | http://www.altera.com/mysupport/                                      |  |  |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m.<br>Pacific Time) | (408) 544-7000 <i>(1)</i><br>(7:00 a.m. to 5:00 p.m.<br>Pacific Time) |  |  |

| Product literature             | http://www.altera.com                                             | http://www.altera.com                                                 |  |  |

| Altera literature services     | lit_req@altera.com (1)                                            | lit_req@altera.com (1)                                                |  |  |

| Non-technical customer service | (800) 767-3753                                                    | (408) 544-7000<br>(7:30 a.m. to 5:30 p.m.<br>Pacific Time)            |  |  |

| FTP site                       | ftp.altera.com                                                    | ftp.altera.com                                                        |  |  |

Note:

(1) You can also contact your local Altera sales office or sales representative.

### Typographic Conventions

This manual uses the typographic conventions shown in Table 3.

| Table 3. Conventions                        |                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type.<br>Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                      |

| Italic Type with Initial<br>Capital Letters | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                                                                  |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PIA}$ , $n + 1$ . Variable names are enclosed in angle brackets (<>) and shown in italic type. Example: < <i>file name</i> >, < <i>project name</i> >. <b>pof</b> file.                                                                |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix _n, e.g., reset_n.                                                                                                                                                                     |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and a., b., c.,                 | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

|                                             | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| $\checkmark$                                | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

| IP                                          | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

### **Table of Contents**

| About this Manual                                           | iii |

|-------------------------------------------------------------|-----|

| How to Find Information                                     |     |

| How to Contact Altera                                       |     |

| Typographic Conventions                                     |     |

| Avalon Bus Specification                                    | 9   |

| General Description                                         |     |

| Features Overview                                           |     |

| Terms and Concepts                                          |     |

| Bus Cycle                                                   |     |

| Bus Transfer                                                |     |

| Streaming Transfer                                          |     |

| Read Transfer with Latency                                  |     |

| SOPC Builder Software & Generation of the Avalon Bus        |     |

| System Module                                               |     |

| Ávalon Bus Module                                           |     |

| Avalon Peripherals                                          |     |

| Peripherals inside the System Module                        |     |

| Peripherals outside the System Module                       |     |

| Master Port                                                 |     |

| Slave Port                                                  | 18  |

| Master-Slave Pair                                           |     |

| PTF File & SOPC Builder Parameters & Switches               | 18  |

| Avalon Bus Transfers                                        |     |

| Master Interface versus Slave Interface                     | 19  |

| Avalon Bus Timing                                           | 20  |

| Avalon Bus Signals                                          | 21  |

| Simultaneous Multi-Master Avalon Bus Considerations         | 23  |

| Avalon Slave Transfers                                      | 23  |

| Avalon Signals for Slave Transfers                          | 24  |

| Slave Read Transfers on the Avalon Bus                      | 26  |

| Fundamental Slave Read Transfer                             | 26  |

| Slave Read Transfer with Fixed Wait States                  | 28  |

| Slave Read Transfer with Peripheral-Controlled Wait States  |     |

| Slave Read Transfer with Setup Time                         |     |

| Slave Write Transfers on the Avalon Bus                     |     |

| Fundamental Slave Write Transfer                            |     |

| Slave Write Transfer with Fixed Wait States                 |     |

| Slave Write Transfer with Peripheral-Controlled Wait States | 41  |

|       | Slave Write Transfer with Setup and Hold Time                    | 43  |

|-------|------------------------------------------------------------------|-----|

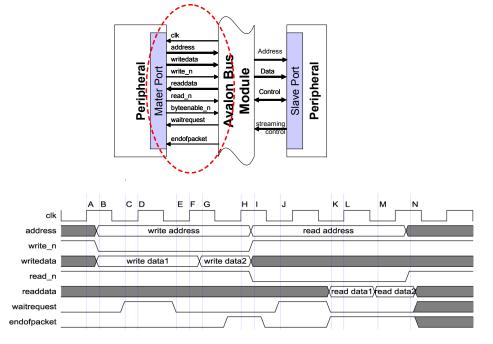

|       | Avalon Master Transfers                                          |     |

|       | Avalon Signals for Master Transfers                              | 46  |

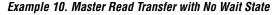

|       | Fundamental Master Read Transfers on the Avalon Bus              |     |

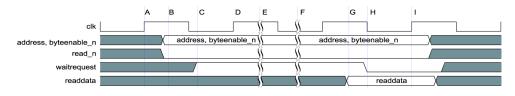

|       | Fundamental Master Write Transfer on the Avalon Bus              | 50  |

|       | Advanced Avalon Bus Transfers                                    | 54  |

|       | Avalon Read Transfers with Latency                               | 54  |

|       | Slave Read Transfer with Fixed Latency                           | 56  |

|       | Slave Read Transfer with Variable Latency                        |     |

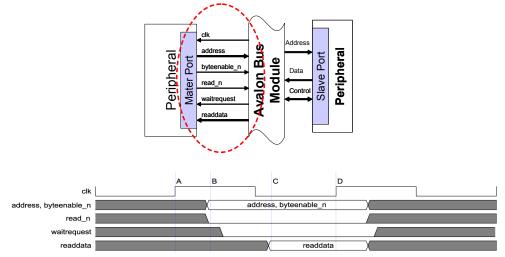

|       | Master Read Transfer with Latency                                | 62  |

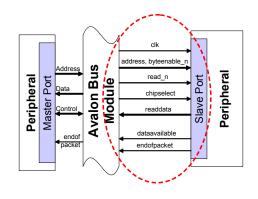

|       | Streaming Transfer                                               |     |

|       | Streaming Slave Transfers                                        | 66  |

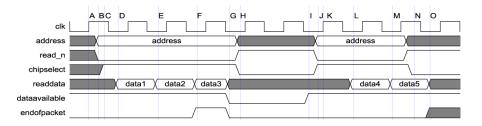

|       | Streaming Slave Read Transfer 67                                 |     |

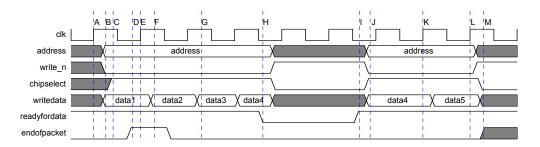

|       | Streaming Slave Write Transfer 70                                |     |

|       | Streaming Master Transfers                                       | 73  |

|       | Avalon Bus Control Signals                                       | 76  |

|       | Interrupt Request Signal                                         | 76  |

|       | Reset Control Logic                                              | 76  |

|       | Begin Transfer Signal                                            | 77  |

|       | Avalon Interface to Off-Chip Devices                             | 78  |

|       | Avalon Tristate Signals for Slave Transfers                      | 78  |

|       | Avalon Tristate Slave Read Transfer without Latency              |     |

|       | Avalon Tristate Slave Read Transfer with Fixed Latency           |     |

|       | Avalon Tristate Slave Write Transfer                             |     |

|       | Avalon Bus Address Alignment Options                             |     |

|       | Address Alignment Overview                                       |     |

|       | Choosing the Address Alignment Assignment for Avalon Peripherals |     |

|       | Native Address Alignment: 32-Bit Master Port                     |     |

|       | Slave Port Between 1 & 8 Bits                                    |     |

|       | Slave Port Between 9 & 16 Bits                                   |     |

|       | Slave Port Between 17 & 31 Bits                                  |     |

|       | Native Address Alignment: 16-Bit Master Port                     |     |

|       | Slave Port Between 1 & 8 Bits                                    |     |

|       | Slave Port Between 9 & 16 Bits                                   |     |

|       | Native Alignment Considerations in Multi-Master System Modules   |     |

|       | Dynamic Bus Sizing                                               |     |

|       | 8-bit Slave Port with Dynamic Bus Sizing                         |     |

|       | 16-bit Slave Port with Dynamic Bus Sizing                        |     |

|       | 32-Bit Slave Port with Dynamic Bus Sizing                        |     |

|       | Connection to External Devices                                   | 100 |

|       |                                                                  |     |

| Index |                                                                  |     |

### **Avalon Bus Specification**

### General Description

The Avalon bus is a simple bus architecture designed for connecting onchip processors and peripherals together into a system–on–a– programmable chip (SOPC). The Avalon bus is an interface that specifies the port connections between master and slave components, and specifies the timing by which these components communicate.

The principal design goals of the Avalon bus were:

- Simplicity Provide an easy-to-understand protocol with a short learning curve.

- Optimized resource utilization for bus logic Conserve logic elements (LEs) inside the Programmable Logic Device (PLD).

- Synchronous operation Integrate well with other user logic that coexists on the same PLD, while avoiding complex timing analysis issues.

Basic Avalon bus transactions transfer a single byte, half-word, or word (8, 16, or 32 bits) between a master and slave peripheral. After a transfer completes, the bus is immediately available on the next clock for another transaction, either between the same master-slave pair, or between unrelated masters and slaves. The Avalon bus also supports advanced features, such as latency-aware peripherals, streaming peripherals and multiple bus masters. These advanced transfer modes allow multiple units of data to be transferred between peripherals during a single bus transaction.

The Avalon bus supports multiple bus masters. This multi-master architecture provides great flexibility in the construction of SOPC systems, and is amenable to high bandwidth peripherals. For example, a master peripheral may perform Direct Memory Access (DMA) transfers, without requiring a processor in the data path to transfer data from the peripheral to memory. Avalon masters and slaves interact with each other based on a technique called slave-side arbitration. Slave-side arbitration determines which master gains access to a slave, in the event that multiple masters attempt to access the same slave at the same time. Slave-side arbitration offers two benefits:

- 1. The details of arbitration are encapsulated inside the Avalon bus. Therefore, the master and slave interfaces are consistent, regardless of the number of masters and slaves on the bus. Each bus master interfaces to the Avalon bus as if it were the only master on the bus.

- 2. Multiple masters can perform bus transactions simultaneously, as long as they do not access the same slave during the same bus cycle.

Avalon has been designed to accommodate the system–on–a – programmable chip (SOPC) environment. The Avalon bus is an active, onchip bus architecture, which consists of logic and routing resources inside a PLD. Some principles of the Avalon architecture are:

- 1. The interface to peripherals is synchronous to the Avalon clock. Therefore, no complex, asynchronous handshaking/acknowledge schemes are necessary. The performance of the Avalon bus (and the overall system) can be measured using standard, synchronous timing analysis techniques.

- 2. All signals are active LOW or HIGH, which facilitates immediate turn-around of the bus. Multiplexers (not tri-state buffers) inside the Avalon bus determine which signals drive which peripheral. Peripherals are never required to tri-state their outputs, even when the peripheral is deselected.

- The address, data and control signals use separate, dedicated ports, which simplifies the design of peripherals. A peripheral does not need to decode address and data bus cycles, and does not need to disable its outputs when it is not selected.

Avalon also includes a number of features and conventions to support automatic generation of systems, busses, and peripherals by the SOPC Builder software.

### Features Overview

*Up to 4GBytes Address Space*—Memory and peripherals may be mapped anywhere within the 32-bit address space.

*Synchronous Interface*—All Avalon signals are synchronized to the Avalon bus clock. This simplifies the relevant timing behavior of the Avalon bus, and facilitates integration with high-speed peripherals.

*Separate Address, Data and Control Lines*—Separate, dedicated address and data paths provide the easiest interface to on-chip user logic. Peripherals do not need to decode data and address bus cycles.

Built-in Address Decoding—The Avalon bus automatically generates Chip Select signals for all peripherals, greatly simplifying the design of Avalon peripherals.

*Multiple Master Bus Architecture*—Multiple master peripherals can reside on the Avalon bus. The Avalon bus automatically generates arbitration logic.

*Wizard-based Configuration*—Easy-to-use graphical wizards guide the user through Avalon bus configuration (adding peripherals, specifying master/slave relationships, defining the memory map). The Avalon bus architecture is generated automatically based on user input from the wizard interface.

*Dynamic Bus Sizing*—The Avalon bus automatically handles the details of transferring data between peripherals with mismatched data widths, allowing peripherals of various widths to interface easily.

Terms and Concepts

Many of the terms and concepts relating to SOPC design are entirely new, or substantially different from traditional, off-chip bus architectures. The designer needs to understand this context in order to understand the Avalon bus specification. The following terms and concepts create a conceptual framework upon which the Avalon bus specification is built. They are used throughout this document.

#### **Bus Cycle**

A bus cycle is a basic unit of one bus clock period, which is defined from rising-edge to rising-edge of the Avalon master clock. Bus signal timing is referenced to the bus cycle clock.

#### **Bus Transfer**

An Avalon bus transfer is a read or write operation of a data object, which may take one or more bus cycles. The transfer sizes supported by the Avalon bus include byte (8-bit), half-word (16-bit) and word (32-bit).

#### **Streaming Transfer**

Streaming transfers create an open channel between a streaming master and streaming slave to perform successive data transfers. This channel allows data to flow between the master-slave pair as data becomes available. The master does not have to continuously access status registers in the slave peripheral to determine whether the slave can send or receive data. Streaming transfers maximize throughput between a master-slave pair, while avoiding data overflow or underflow on the slave peripheral. This is especially useful for DMA transfers.

#### **Read Transfer with Latency**

Read transfer with latency increase the bandwidth efficiency to synchronous peripherals that require several cycles of latency for the first access, but can return data every bus cycle thereafter. Latent transfers allow a master to issue a read request, move on to an unrelated task, and receive the data later. The unrelated task can be issuing another read transfer, even though data from the previous transfer hasn't yet returned. This is beneficial for instruction fetch operations and DMA transfers, in which access to sequential addresses is the norm. In these cases, the CPU or the DMA master may prefetch expected data, thereby keeping the synchronous memory active and reducing the average access latency.

#### SOPC Builder Software & Generation of the Avalon Bus

SOPC Builder is a system generation and integration tool developed by Altera. SOPC Builder generates the system module, which is the on-chip circuitry that comprises the Avalon bus, master peripherals, and slave peripherals. SOPC Builder has a graphical user interface for adding master and slave peripherals to the system module, configuring the peripherals, and then configuring the Avalon bus to connect peripherals together. With this information, SOPC Builder automatically creates and connects HDL modules, that implements all or part of the user's PLD design.

See the *SOPC Builder Data Sheet* for more information about the system module.

#### System Module

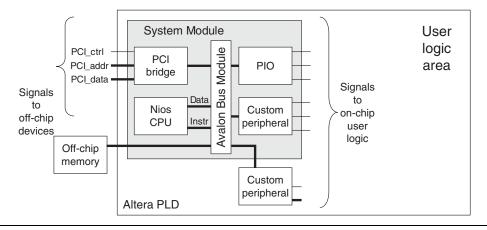

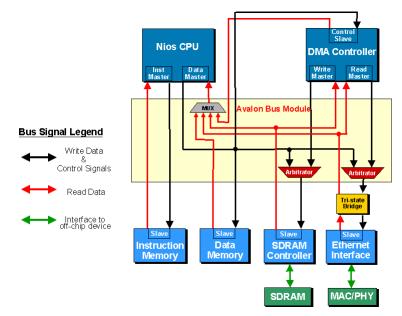

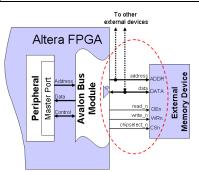

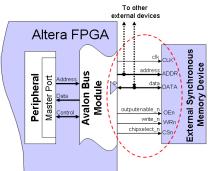

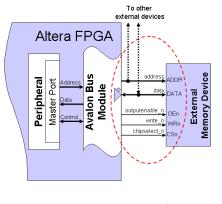

Consider the structure of a user-defined system on a programmable chip, part of which is automatically generated by SOPC Builder. The entire system is implemented on an Altera PLD, as shown in Figure 1.

Figure 1. System Module Integrated with User Logic into an Altera PLD

For purposes of this document, system module refers to the portion of the design that was automatically generated by SOPC Builder. The system module contains at least one Avalon master peripheral and the entire Avalon bus module. The system module usually contains several Avalon slave peripherals, such as UARTs, timers or PIOs. The logic external to the system module may contain custom Avalon peripherals and other custom logic unrelated to the system module.

The system module must be connected to the designer's PLD design. The ports on the system module will vary, depending on which peripherals are included in the system module and which settings were made in SOPC Builder. These ports may include direct connections to the Avalon bus, and user-defined ports to peripherals inside the system module.

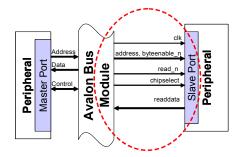

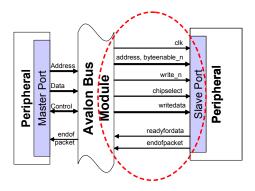

#### **Avalon Bus Module**

The Avalon bus module is the backbone of an system module. It is the main path of communication between peripherals components in an SOPC design. The Avalon bus module is the sum of all control, data and address signals and arbitration logic that connect together the peripheral components making up the system module. The Avalon bus module implements a configurable bus architecture, which changes to fit the interconnection needs of the designer's peripherals. The Avalon bus module is generated automatically by SOPC Builder, so that the system designer is spared the task of connecting the bus and peripherals together. The Avalon bus module is very rarely used as a discrete unit, because the system designer will almost always use SOPC Builder to automate the integration of processors and other Avalon bus peripherals into a system module. The designer's view of the Avalon bus module usually is limited to the specific ports that relate to the connection of custom Avalon peripherals.

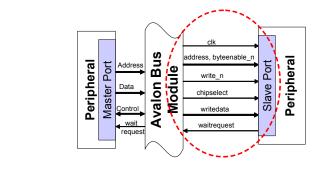

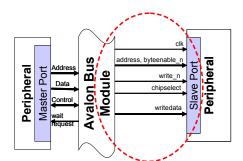

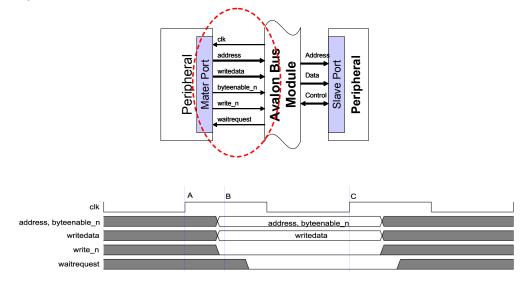

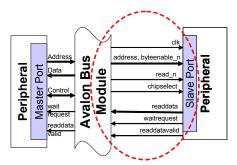

The Avalon bus module (an Avalon bus) is a unit of active logic that takes the place of passive, metal bus lines on a physical PCB. (See Figure 2). In this context, the ports of the Avalon bus module could be thought of as the pin connections for all peripheral devices connected to a passive bus. This manual defines only the ports, logical behavior and signal sequencing that comprise the interface to the Avalon bus module. It does not specify any electrical or physical characteristics of a physical bus.

Figure 2. Avalon Bus Module Block Diagram - An Example System

The Avalon bus module provides the following services to Avalon peripherals connected to the bus:

- Data-Path Multiplexing—Multiplexers in the Avalon bus module transfer data from the selected slave peripheral to the appropriate master peripheral.

- Address Decoding—Address decoding logic produces chip-select signals for each peripheral. This simplifies peripheral design, because individual peripherals do not need to decode the address lines to generate chip-select signals.

- Wait-State Generation—Wait-state generation extends bus transfers by one or more bus cycles, for the benefit of peripherals with special synchronization needs. Wait states can be generated to stall a master peripheral in cases when the target slave peripheral cannot respond in a single clock cycle. Wait states can also be generated in cases when read-enable and write-enable signals have setup or hold time requirements.

- Dynamic Bus Sizing—Dynamic bus sizing hides the details of interfacing narrow peripherals to a wider Avalon bus, or vice versa. For example, in the case of a 32-bit master read transfer from a 16-bit memory, dynamic bus sizing would automatically execute two slave read transfers to fetch 32 bits of data from the 16-bit memory device. This reduces the logic and/or software complexity in the master peripheral, because the master does not have to worry about the physical nature of the slave peripheral.

- Interrupt-Priority Assignment—When one or more slave peripherals generate interrupts, the Avalon bus module passes the (prioritized) interrupts to appropriate master peripherals, along with the appropriate interrupt request (IRQ) number.

- Latent Transfer Capabilities—The logic required to perform transfers with latency between master-slave pairs is contained inside the Avalon bus module.

- Streaming Read and Write Capabilities—The logic required to allow streaming transfers between master-slave pairs is contained inside the Avalon bus module.

#### **Avalon Peripherals**

An Avalon peripheral on the Avalon bus is a logical device—either on-chip or off-chip—that performs some system-level task, and communicates with other system components through the Avalon bus. Peripherals are modular system components, and may be added or removed at design time, depending on the requirements of the system.

Avalon peripherals can be memories and processors, as well as traditional peripheral components, such as a UART, PIO, timer or bus bridge. Any user logic can also be an Avalon peripheral, as long as it provides address, data and control signal interfaces to the Avalon bus as described in this document. A peripheral connects to specific ports on the Avalon bus module allocated for that peripheral. The peripheral may also have user-defined ports in addition to the Avalon address, data and control signals. These signals connect to custom logic external to the system module.

The roles of Avalon peripherals are classified as either a master or slave. A master peripheral is a peripheral that can initiate bus transfers on the Avalon bus. A master peripheral has at least one master port ("Master Port" on page 17) which connects to the Avalon bus module. A master peripheral may also have a slave port ("Slave Port" on page 18), which allows the peripheral to receive bus transfers initiated by other master peripherals on the Avalon bus. A slave peripheral is a peripheral that only accepts bus transfers from the Avalon bus, and cannot initiate bus transfers. Slave peripherals, such as memory devices or UARTs, usually have only one slave port, which connects to the Avalon bus module.

In the SOPC environment, it is important to make the distinction between the following types of peripherals, which may be either Avalon bus masters or slaves.

#### Peripherals inside the System Module

If SOPC Builder finds a peripheral in a peripheral library, or if the designer specifies the location of a custom peripheral design file, then SOPC Builder automatically connects the peripheral to the Avalon bus module. Such a peripheral is referred to as a peripheral inside the system module, and is treated as a piece of the system module. The details of connecting the address, data and control ports to the Avalon bus module are hidden from the user. Any additional non-Avalon ports on the peripheral are presented to the outside world as ports on the system module. These ports may connect directly to physical device pins, or may connect to the ports of other on-chip modules.

#### Peripherals outside the System Module

An Avalon bus peripheral can also exist external to the system module. This peripheral is referred to as a peripheral outside the system module. A designer may chose to leave the module outside the system module for several reasons:

- The peripheral may exist physically outside the PLD.

- The peripheral may require some glue logic to connect it to the Avalon bus signals.

- The peripheral design may not be complete at the time the system module is generated.

In this case, the appropriate Avalon bus module signals are presented to the outside world (and to the specific peripheral) as ports on the system module.

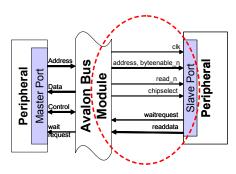

#### **Master Port**

A master port is the collection of ports on a master peripheral used to initiate transfers on the Avalon bus. The master port connects directly to the Avalon bus module. In practice, a master peripheral may have one or more master ports, as well as a slave port. The interdependence of these master and slave ports is dependent on the peripheral design. However, individual bus transfers on these master or slave ports always conform to this document. Throughout this document, a master transfer refers to an Avalon bus transfer from the perspective of a single master port.

#### **Slave Port**

A slave port is the collection of ports on a peripheral to accept Avalon bus transfers from the master port on another Avalon peripheral. The slave port connects directly to the Avalon bus module. Master peripherals may also have a slave port, which allows the peripheral to accept transfers from other masters on the Avalon bus. Throughout this document, a slave transfer refers to an Avalon bus transfer from the perspective of a single slave port.

#### **Master-Slave Pair**

A master-slave pair is the combination of a master port and a slave port that are connected via the Avalon bus module. Structurally, these master and slave ports connect to their appropriate ports on the Avalon bus module. Effectively, the master port's control and data signals pass through the Avalon bus module, and interact with the slave port. Connections between master and slave ports (thus creating master-slave pairs) are specified in SOPC Builder.

#### PTF File & SOPC Builder Parameters & Switches

The configuration of the Avalon bus and peripherals can be specified using the wizard-based SOPC Builder graphical user interface (GUI). Through this GUI the user specifies various parameters and switches, which are then used to generate a system PTF file. The PTF file is a text file that fully defines:

- Parameters that define the structure and/or functionality of the Avalon bus module.

- Parameters for each peripheral that define its structure and/or functionality.

- The master/slave role of each peripheral.

- The ports (such as read enable, read data, write enable, write data) present on each peripheral.

- The arbitration mechanism for each slave port that can be accessed by multiple master ports.

The PTF file is then passed to an HDL generator that creates the actual register transfer level (RTL) description of the system module.

See the *SOPC Builder Data Sheet* and the *SOPC Builder PTF File Reference Manual* for additional information about the system PTF files.

### Avalon Bus Transfers

The Avalon bus specification defines the signals and timing required to transfer data between a master port and a slave port via the Avalon bus module. The signals that comprise the interface between the Avalon bus module and the peripheral are different, depending on the type of transfer. Foremost, the interface is different for master transfers and slave transfers, giving rise to the distinct definitions of a slave port and a master port. Furthermore, the exact type and number of signals required will vary, based on assignments made in the system PTF file.

The Avalon bus specification offers a variety of options to tailor the bus signals and timing to the needs of different types of peripherals. Fundamental Avalon bus transfers move a single unit of data per bus transfer between a master-slave pair. The bus transfer can be extended with wait states to accommodate slow peripherals. Streaming transactions along with simultaneous multi-master capabilities accommodate high-bandwidth peripherals. Peripherals can also use a combination of transaction types. The sequencing of signals for all Avalon slave transfers are derived from the fundamental slave read transfer and fundamental slave write transfer. Likewise, the fundamental master read and master write transfers are the basis for all Avalon master transfers.

#### Master Interface versus Slave Interface

When discussing Avalon bus transfers, it is important to pay attention to which side of the bus is the focus: the master port interface or the slave port interface. The signals output from a master port on the Avalon bus module may be very different from the corresponding signals that are input into the slave port on the target peripheral.

The signal activity on the slave side is always the result of a master peripheral initiating a bus transfer, but the actual slave port input signals do not come directly from the master port. The Avalon bus module relays the signals from the master port, and custom-tailors the signals (e.g., inserts wait states; arbitrates between contending masters) to the needs of the slave peripheral.

For this reason, the discussion of Avalon bus transfers is separated into master transfer types and slave transfer types. Most designers will be interested only in slave transfers, because the custom peripherals they design (if any) will most likely be slave peripherals. In this case, the designer considers only the signaling between the Avalon bus module and the custom peripheral. The discussion of master transfers is only relevant in the event that a designer creates a master peripheral.

#### Avalon Bus Timing

The Avalon bus is a synchronous bus interface, clocked by a master Avalon bus clock. All bus transfers occur synchronous to the Avalon bus clock. All bus transfers initiate on a rising clock edge, and terminate after valid data is captured on (or before) a subsequent rising clock edge.

A synchronous bus interface does not necessarily mean that all Avalon bus signals are registered. Notably, the Avalon chipselect signal is combinatorial, based on the outputs of registers that are synchronous to the Avalon bus clock, clk. Therefore, peripherals must not be edge sensitive to Avalon signals, because Avalon signals may transition multiple times before they stabilize. As with any synchronous design, Avalon bus peripherals must function only in response to signals that are stable at the rising edge of clk, and output stable signals at the rising edge of clk.

It is possible to interface asynchronous peripherals such as off-chip, asynchronous memory to the Avalon bus module, but there are a few design considerations. Due to the synchronous operation of the Avalon bus module, Avalon signals toggle only at intervals equal to the period of the Avalon bus clock. Also, if an asynchronous peripheral's outputs are connected directly to the Avalon bus module, the designer must make sure that the output signals are stable before the rising edge of clk.

The Avalon bus specification makes no attempt to dictate how signals transition between clock edges. Toggling signals are triggered by the Avalon bus clock, and that signals must stabilize before the clock edge when they are captured. For this reason, the Avalon bus timing diagrams in this document are devoid of explicit timing information. The exact timing of signals toggling and stabilizing between clock edges will vary, depending upon the characteristics of the Altera PLD selected to implement the system. By the same token, there is no inherent maximum performance of the Avalon bus. After synthesis and place-and-route of the system module for a specific device, the designer must perform standard timing analysis on the system module to determine the maximum speed at which Avalon bus transfers can be performed.

#### Avalon Bus Signals

Because the Avalon bus is an on-chip bus architecture synthesized from HDL files, special attention must be given to the connections between the Avalon bus module and Avalon peripherals. The situation is very different from a passive, off-chip bus architecture in which all peripherals share access to a pre-defined and constant group of physical metal wires. In the case of the Avalon bus, SOPC Builder must know exactly what Avalon ports are present on each peripheral so that it can connect the peripherals to Avalon bus module. Furthermore, it must know the name of each port and the role of each port. The name and role for each port on an Avalon peripheral is declared in the system PTF file.

The Avalon bus specification does not mandate the existence of any port on an Avalon peripheral. It only defines the possible types of signals (such as address, data, clock) that can exist on a peripheral. Each port on a peripheral is assigned a valid Avalon signal type, which determines the port's role. A port may also be user-defined, in which case SOPC Builder does not connect the port to the Avalon bus module. Fundamentally, the Avalon signal types are classified as either slave port signals or master port signals. Therefore, the signal types used by a peripheral are determined first and foremost by the master/slave role of the port. Each master or slave port may have up to one of each signal type. The set of signal types used by an individual master or slave port is dependent on the design of the peripheral. For example, the design for an output-only PIO slave peripheral would define only ports for write transfers (the output direction), but no ports for read transfers. Such a peripheral also probably would have no use for an Interrupt Request (IRQ) output, even though an IRQ output is an allowed signal type for a slave port.

The Avalon bus specification does not dictate a naming convention for the ports on an Avalon peripheral. The role of each port is well defined, but the name of the port is defined by the peripheral design. The port may be named the same as its signal type, or it may be named differently to comply with a system-wide naming convention. The discussion of Avalon bus transfers in the following sections refers to Avalon signals as, for example, the readdata signal or the irq signal. The name of the signal type has been used here as the port name, but the actual names given to ports on peripherals in the System Module may be different. Table 1 shows a partial list of the signal types available to an Avalon slave port as an example. The signal direction is from the perspective of the peripheral. For example, the clock signal clk (listed as an input) is an *input* to the slave peripheral, but it is an *output* from the Avalon bus module.

| Table 1. Partial Lis | Table 1. Partial List of Avalon Slave Signals |           |          |                                                                                                                                                                           |  |

|----------------------|-----------------------------------------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Signal Type          | Width                                         | Direction | Required | Description                                                                                                                                                               |  |

| clk                  | 1                                             | in        | no       | Global clock signal for the system module<br>and Avalon bus module. All bus transactions<br>are synchronous to clk. Only asynchronous<br>slave ports can omit clk.        |  |

| address              | 1 - 32                                        | in        | no       | Address lines from the Avalon bus module.                                                                                                                                 |  |

| read                 | 1                                             | in        | no       | Read request signal to slave. Not required if<br>the slave never outputs data to a master. If<br>used, readdata must also be used.                                        |  |

| readdata             | 1 – 32                                        | out       | no       | Data lines to the Avalon bus module for read transfers. Not required if the slave never outputs data to a master. If used, read signal must also be used.                 |  |

| write                | 1                                             | in        | no       | Write request signal to slave. Not required if<br>the slave never receives data from a master.<br>If used, writedata must also be used.                                   |  |

| writedata            | 1 – 32                                        | in        | no       | Data lines from the Avalon bus module for<br>write transfers. Not required if the slave never<br>receives data from a master. If used, write<br>signal must also be used. |  |

| irq                  | 1                                             | out       | no       | Interrupt request. Slave asserts irg when it needs to be serviced by a master.                                                                                            |  |

The signal types listed in Table 1 are active high. However, the Avalon bus also offers the negated version of each signal type. By appending "\_n" to the signal type name (e.g., irq\_n, read\_n) in the PTF declaration, the corresponding port is declared active low. This is useful for many off-chip peripherals that use active-low logic.

The Avalon bus signals and their operation is the same, whether a peripheral is implemented inside the system module or outside the system module. In the inside case, SOPC Builder automatically connects the peripheral's master or slave port to the Avalon bus module. In the outside case, the designer must manually connect the master or slave port to the system module. In either case, the Avalon bus signals behave the same.

For additional System Builder and PTF file information see the SOPC Builder Data Sheet. and the SOPC Builder PTF File Reference Manual.

#### Simultaneous Multi-Master Avalon Bus Considerations

The Avalon bus accommodates multiple master ports connected to the Avalon bus module. However, no special signals external to the Avalon bus module are used to implement simultaneous multimaster Avalon bus functionality. Slave-side arbitration logic inside the Avalon bus module arbitrates conflicts when multiple master peripherals attempt to access the same slave peripheral at the same time. The arbitration scheme is entirely hidden from Avalon bus peripherals. Therefore, the protocol for Avalon bus transfers—as perceived by master and slave ports—is the same, whether arbitration is used or not.

In other words, slave ports are not aware that multiple masters have simultaneously requested a bus transfer. Likewise, a master peripheral that is forced to wait by the arbitration logic is not aware of the other victorious master. The master port simply sees its waitrequest signal asserted, and knows that it must wait until the target slave is ready to proceed with the bus transfer. Hiding the details of arbitration inside the Avalon bus module greatly simplifies peripheral design, because any Avalon peripheral can be used both in single-master and multi-master architectures.

See AN 184: Simultaneous Multi-Mastering with the Avalon Bus for more information.

The following sections discuss bus transfers between a slave port and the Avalon bus. From an abstract, system-level viewpoint, master peripherals exchange data with slave peripherals. However, from the viewpoint of a slave peripheral, data is transferred between the peripheral's slave port and the Avalon bus module. In the following discussion of bus transfers with slave ports, it is assumed that a master peripheral somewhere on the Avalon bus has successfully initiated a transfer on the master side of the Avalon bus module. As a result, the Avalon bus module then initiates the transfer with the appropriate slave port. The interface between the Avalon bus module and the slave port is the exclusive focus of this section.

### Avalon Slave Transfers

#### **Avalon Signals for Slave Transfers**

Table 2 below lists the signal types that interface a peripheral's slave port to the Avalon bus module. The signal direction is from the perspective of the slave port. Not all of the signal types listed in Table 2 will be present on all peripherals, depending on the peripheral design and the ports declared in the PTF file. Table 2 gives a brief description of which signals are required and under what circumstances

| Signal Type   | Width   | Direction | Required | Description                                                                                                                                                               |

|---------------|---------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| clk           | 1       | in        | no       | Global clock signal for the system module and<br>Avalon bus module. All bus transactions are<br>synchronous to clk. Only asynchronous slave<br>ports can omit clk.        |

| reset         | 1       | in        | no       | Global reset signal. Implementation is peripheral-specific.                                                                                                               |

| chipselect    | 1       | in        | yes      | Chip select signal to the slave. The slave port<br>should ignore all other Avalon signal inputs unless<br>chipselect is asserted.                                         |

| address       | 1 - 32  | in        | no       | Address lines from the Avalon bus module.                                                                                                                                 |

| begintransfer | 1       | in        | no       | Asserted during the first bus cycle of each new Avalon bus transfer. Usage is peripheral-specific.                                                                        |

| byteenable    | 0, 2, 4 | in        | no       | Byte-enable signals to enable specific byte lane(s)<br>during transfers to memories of width greater than<br>8 bits. Implementation is peripheral-specific.               |

| read          | 1       | in        | no       | Read request signal to slave. Not required if the slave never outputs data to a master. If used, readdata must also be used.                                              |

| readdata      | 1 – 32  | out       | no       | Data lines to the Avalon bus module for read<br>transfers. Not required if the slave never outputs<br>data to a master. If used, read signal must also be<br>used.        |

| write         | 1       | in        | no       | Write request signal to slave. Not required if the slave never receives data from a master. If used, writedata must also be used.                                         |

| writedata     | 1 – 32  | in        | no       | Data lines from the Avalon bus module for write<br>transfers. Not required if the slave never receives<br>data from a master. If used, write signal must<br>also be used. |

| Signal Type   | Width | Direction | Required | Description                                                                                                                                           |

|---------------|-------|-----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| readdatavalid | 1     | out       | no       | Used only by slaves with variable latency. Marks<br>the rising clock edge when the slave asserts valid<br>readdata.                                   |

| waitrequest   | 1     | out       | no       | Used to stall the Avalon bus module when slave port is not able to respond immediately.                                                               |

| readyfordata  | 1     | out       | no       | Signal for streaming transfers. Indicates that the streaming slave can receive data.                                                                  |

| dataavailable | 1     | out       | no       | Signal for streaming transfers. Indicates that the streaming slave has data available.                                                                |

| endofpacket   | 1     | out       | no       | Signal for streaming transfers. May be used to<br>indicate an "end of packet" condition to the master<br>port. Implementation is peripheral-specific. |

| irq           | 1     | out       | no       | Interrupt request. Slave asserts irg when it needs to be serviced by a master.                                                                        |

| resetrequest  | 1     | out       | no       | A reset signal allowing a peripheral to reset the entire system module.                                                                               |

In the following discussions of Avalon slave transfers, the read, write and byteenable signals are used in their active-low form, which is similar to the traditional convention of using active-low read enable, write enable and byte enable signals. Note the following:

- These signals appear in the form read\_n, write\_n and byteenable\_n.

- Any port of an Avalon signal type may be used with active high or low polarity, based on the port's declaration in the PTF file.

#### **Slave Read Transfers on the Avalon Bus**

In the discussions of read transfers below, it is important to realize that under realistic circumstances, bus transfers are not isolated events. They typically happen in continuous succession. For example, a slave read transfer may immediately precede or follow an unrelated write transfer. During the read transfer, the target peripheral's read\_n and chipselect signals are necessarily asserted, as shown in the timing diagrams. However, after the read transfer terminates, chipselect and read\_n may remain asserted if another bus transfer with this slave port follows on the next bus cycle. The timing diagrams below show undefined values on the slave port signals before and after the read transfer. Fundamental slave read transfers have no latency.

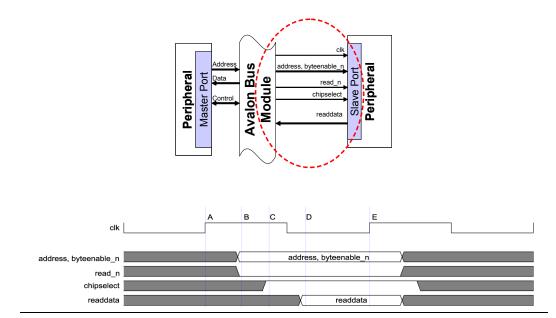

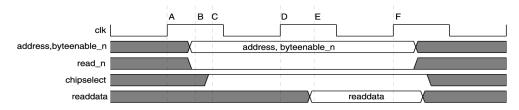

#### Fundamental Slave Read Transfer

The fundamental slave read transfer is the basis for all Avalon slave read transfers. All other slave read transfer modes use a super set of the fundamental signals, and implement a variation of the fundamental slave read timing. The fundamental slave read transfer is initiated by the Avalon bus module, and transfers one unit of data, the full width of the peripheral's data port, from the slave port to the Avalon bus module. Fundamental slave read transfers have no latency.

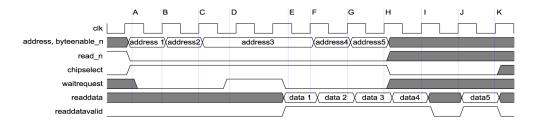

Example 1 shows an example of the fundamental read transfer. In the fundamental Avalon read transfer, the bus transfer starts on a rising clock edge, no wait states are incurred, and the read transfer completes on the next rising clock edge. For the transfer to complete in a single bus cycle, the target peripheral must immediately and asynchronously output the contents of the addressed location to the Avalon bus module.

On the first rising edge of clk, the Avalon bus passes the address, byteenable\_n, and read\_n signals to the target peripheral. The Avalon bus module decodes address internally, generates a chip select and drives the combinatorial chipselect signal to the slave port. Once chipselect is asserted, the slave port drives out its readdata as soon as it is available. Finally, the Avalon bus module captures the readdata on the next rising edge of the clock.

#### **Example 1. Fundamental Slave Read Transfers**

| This Example Demonstrates                     | Relevant PTF Parameters |

|-----------------------------------------------|-------------------------|

| Read transfer from an asynchronous peripheral |                         |

| Zero wait states                              | Read_Wait_States = "0"  |

| Zero setup                                    | Setup_Time = "0"        |

#### Example 1 Time Reference Description

- (A) First bus cycle starts on the rising edge of clk.

- (B) Registered outputs address and read\_n from Avalon bus to slave are valid

- (C) Avalon bus decodes address & asserts valid chipselect to slave.

- (D) Slave port returns valid data during the first bus cycle.

- (E) Avalon bus captures readdata on the next rising edge of clk, and the read transfer ends here. The next bus cycle could be the start of another bus transfer.

This fundamental read transfer with zero wait states is appropriate only for truly asynchronous peripherals. The target peripheral must present data to the Avalon bus immediately when the peripheral is selected and/or the address changes. For the transfer to work properly, readdata's output must be valid and stable by the next rising clock edge. Synchronous peripherals that register the input or output ports cannot use the fundamental slave read transfer with zero wait states. Most on-chip peripherals will use a synchronous interface that requires at least one clock to capture data. This necessitates at least one wait state during the read transfer unless the peripheral is latency aware. See "Avalon Read Transfers with Latency" on page 54 for more information.

The byte enable lines byteenable\_n may be connected to the peripheral's slave port. Interpretation of byteenable\_n is peripheral dependent for slave read transfers. In the simplest case, the slave port ignores byteenable\_n, and always drives all byte lanes whenever read\_n is asserted. The Avalon bus module captures the full bit width of the readdata port every read transfer. Therefore, if an individual byte lane is not enabled during a read transfer, the value returned to the Avalon bus module is undefined, which may or may not affect the master that ultimately receives the data.

When chipselect is deasserted, all other input signals should be ignored. The slave port outputs may be driven or left undefined when the slave port is not selected. The chipselect signal driven to the target peripheral may be combinatorial, based on registered address values. Furthermore, a low-to-high edge on chipselect or a high-to-low edge on read\_n cannot be used as a start read transfer trigger, because such an edge is not guaranteed.

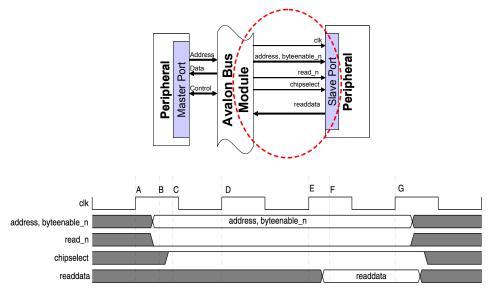

#### Slave Read Transfer with Fixed Wait States

The ports used for a slave read transfer with fixed wait states are identical to those used for a fundamental read transfer. The difference is in the timing of signals only. Slave read transfers with wait states are useful for peripherals that cannot present data within a single clock cycle. For example, with one fixed wait state specified, the Avalon bus module presents a valid address and control, but waits for one clock cycle before capturing the peripheral's data. Fixed wait states for a peripheral are declared in the PTF file. They are fixed because the Avalon bus module waits a fixed number of bus cycles every read transfer. Example 2 shows an example slave read transfer with one wait state. The Avalon bus module presents address, byteenable\_n, read\_n and chipselect during the first bus cycle. Because of the wait state, the peripheral does not have to present readdata within the first bus cycle; the first bus cycle is the first (and only) wait state. The slave port may capture address and control signals at any time. On-chip, synchronous peripherals will probably capture address and control on the rising edge of clk at the start of the second bus cycle (the end of the wait state). During the second bus cycle, the target peripheral presents its readdata to the Avalon bus module. On the third and final rising clock edge, the Avalon bus module captures readdata from the slave port, and completes the transfer.

#### Example 2. Slave Read Transfer with One Fixed Wait State (Part 1 of 2)

| This Example Demonstrates                   | Relevant PTF Parameters |

|---------------------------------------------|-------------------------|

| Read transfer from a synchronous peripheral |                         |

| 1 fixed wait state                          | Read_Wait_States = "1"  |

| No setup time                               | Setup_Time = "0"        |

#### Example 2: Slave Read Transfer with One Fixed Wait State (Part 2 of 2)

#### Example 2 Time Reference Description

- (A) First bus cycle starts on the rising edge of clk.

- (B) Registered outputs address and read\_n from Avalon bus to slave are valid

- (C) Avalon bus decodes address & asserts chipselect.

- (D) Rising edge of clk marks the end of the first and only wait-state bus cycle. If the slave port is synchronous, it probably captures address, read\_n & chipselect on this rising edge of clk.

- (E) Peripheral presents valid readdata during the second bus cycle.

- (F) Avalon bus module captures readdata on the rising edge of clk, and the read transfer ends here. The next bus cycle could be the start of another bus transfer

Read transfers with a single wait state are frequently used for synchronous, on-chip peripherals. Sound PLD design methodology dictates that the interface between modules should be synchronized with registers. Adding a wait state makes the transfer more amenable to PLD design, because the peripheral can capture synchronous signals address, byteenable\_n, read\_n and chipselect on the rising edge of clk after chipselect is asserted. The target peripheral then has at least one full bus cycle to present data back to the Avalon bus module. For higher bandwidth with pipelined read transactions, see "Avalon Read Transfers with Latency" on page 54. Example 3 on shows a read transfer with multiple fixed wait states. This case is almost identical to Example 2 on page 29, except that the Avalon Bus now waits for more than one bus cycle before sampling the readdata from the slave peripheral.

#### Example 3. Slave Read Transfer with Multiple Fixed Wait States

| This Example Demonstrates                   | Relevant PTF Parameters |

|---------------------------------------------|-------------------------|

| Read transfer from a synchronous peripheral |                         |

| 2 fixed wait states                         | Read_Wait_States = "2"  |

| No setup time                               | Setup_Time = "0"        |

#### **Example 3 Time Reference Description**

- (A) First bus cycle starts on the rising edge of clk.

- (B) Registered outputs address and read\_n from Avalon bus to slave are valid

- (C) Avalon bus decodes address then asserts chipselect.

- (D) Rising edge of clk marks the end of the first wait-state bus cycle. If the slave port is synchronous, it probably captures address, read\_n & chipselect on this rising edge of clk.

- (E) Rising edge of clk marks the end of the second (and last) wait state.

- (F) Peripheral presents valid readdata sometime during the third cycle.

- (G) Avalon bus module captures readdata on the rising edge of clk, and the read transfer ends here. The next bus cycle could be the start of another bus transfer.

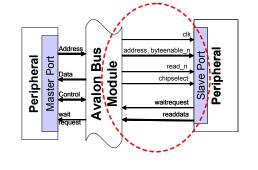

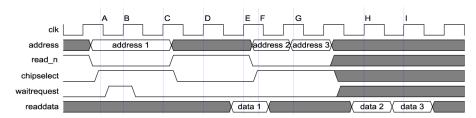

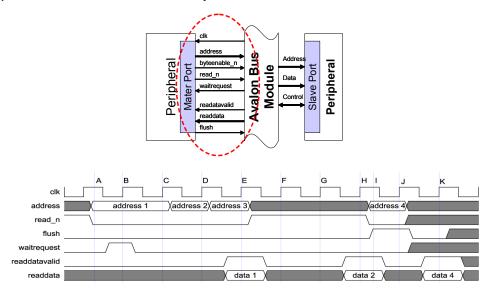

#### Slave Read Transfer with Peripheral-Controlled Wait States

Peripheral-controlled wait states allow a target peripheral to stall the Avalon bus module for as many bus cycles as required to present data. Using this transfer mode, a peripheral can take a variable amount of time to present data to the Avalon bus module.

Example 4 on page 33 shows slave read transfer with peripheralcontrolled wait states. The peripheral-controlled wait state mode uses the waitrequest signal, which is an output from the slave port. After read\_n is asserted to the slave port, the slave port must return waitrequest within the first bus cycle if it wishes to extend the read transfer. When asserted, waitrequest stalls the Avalon bus module and prevents it from capturing readdata. The Avalon bus module will capture readdata on the next rising edge of clk after waitrequest is deasserted.

The Avalon bus module does not have a time-out feature to limit how long the slave port can stall. When the Avalon bus module is stalled, somewhere in the system module there is a master peripheral that is stalled as well, waiting for the requested data to come back from the addressed slave peripheral. A slave port could permanently "hang" the master port. Therefore, the peripheral designer must ensure that a slave peripheral does not assert waitrequest indefinitely.

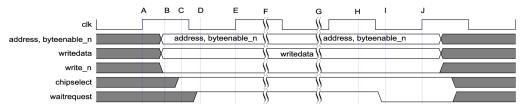

| This Example Demonstrates                      | Relevant PTF Parameters                    |

|------------------------------------------------|--------------------------------------------|

| Read transfer from synchronous peripheral      |                                            |

| More than one peripheral-controlled wait state | Read_Wait_States = "peripheral_controlled" |

| No setup                                       | Setup_Time ="0"                            |

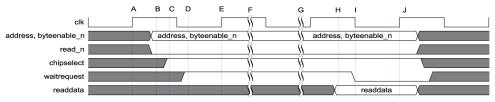

#### Example 4. Slave Read Transfer with Peripheral-Controlled Wait States

#### **Example 4 Time Reference Description**

- (A) First bus cycle starts on the rising edge of clk.

- (B) Registered outputs address and read\_n from Avalon bus to slave are valid

- (C) Avalon bus decodes address then asserts chipselect.

- (D) Slave port asserts waitrequest before the next rising edge of clk.

- (E) Avalon bus module samples waitrequest at the rising edge of clk. waitrequest is asserted. so readdata is not captured on this clock edge.

(F-G) With waitrequest asserted throughout, an infinite number of bus cycles elapse.

- H) Slave port presents valid readdata.

- (I) Slave port deasserts waitrequest.

- (J) Avalon bus module captures readdata on the next rising edge of clk, and the read transfer ends here. The next bus cycle could be the start of another bus transfer.

When peripheral-controlled wait states are specified, the following restrictions apply to other bus transfer modes. These restrictions apply only to transfers with this specific slave port, not to any other peripheral connected to the Avalon bus module.

If peripheral-controlled wait states are specified, setup and hold wait states cannot be used. In almost all cases, a peripheral that can generate the waitrequest signal will be on-chip and synchronous causing setup and hold time considerations unnecessary.

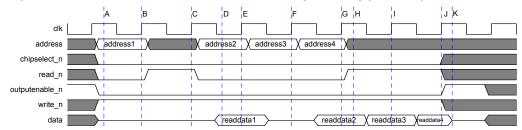

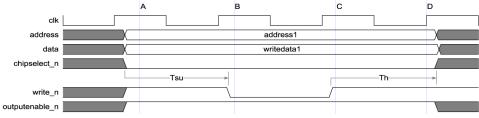

#### Slave Read Transfer with Setup Time

The Avalon bus module automatically accommodates setup time requirements for each slave port, based on declarations made in the PTF file. The master peripheral that initiates the read transfer does not need to consider the setup and hold requirements of each slave port. The ports used for a read transfer with setup time are identical to those used for a fundamental read transfer. The difference is in the timing of signals only.

Setup time is generally used for off-chip peripherals that require address and chipselect signals to be stable for a period of time before the read enable signal is asserted. A nonzero setup time of N means that, after address, byteenable\_n and chipselect signals are presented to the slave port, there is a delay of N bus cycles before read\_n is asserted. Note that chipselect is not affected by the setup time. If the peripheral requires a setup time for both read\_n and chipselect, then the designer must manually add the appropriate logic (one AND gate) to the interface.

The total number of bus cycles to complete the bus transfer depends on setup and wait-state bus cycles. For example, a peripheral with Setup\_Time="2" and Read\_Wait\_States="3" will take 6 bus cycles to complete the transfer:

- 2 setup bus cycles plus

- 3 wait-state bus cycles plus

- 1 bus cycle to capture data

Example 5 shows a slave read transfers with one bus cycle of setup and one fixed wait state.

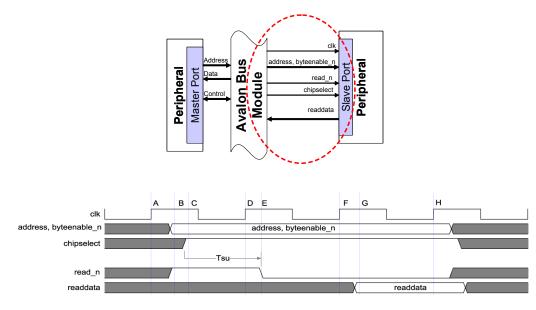

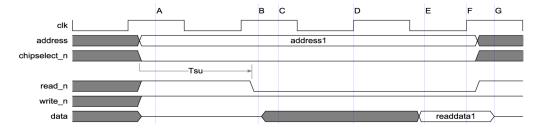

#### Example 5. Slave Read Transfer with Setup Time

| This Example Demonstrates                 | Relevant PTF Parameters |

|-------------------------------------------|-------------------------|

| Read transfer from synchronous peripheral |                         |

| 1 bus cycle of setup time                 | Setup_Time = "1"        |

| 1 fixed wait state                        | Read_Wait_States = "1"  |

#### **Example 5 Time Reference Description**

- (A) First bus cycle on the rising edge of clk.

- (B) Registered output address and byteenable\_n from the Avalon bus module are valid. read\_n remains deasserted.

- (C) Avalon bus module decodes address then asserts chipselect.

- (D) Rising edge of clk defines the end of the setup-time bus cycle (Tsu), and the start of the wait-state bus cycle.

- (E) Avalon bus module asserts read\_n

- (F) Rising edge of clk marks the end of the wait-state bus cycle.

- (G) Peripheral presents valid readdata.

- (H) Avalon bus module captures readdata at the rising edge of clk, and the read transfer ends here. The next bus cycle could be the start of another bus transfer.

When setup time is specified for a peripheral on the Avalon bus, the following restrictions apply to other bus transfer modes. These restrictions apply only to this slave port, not to other peripherals connected to the Avalon bus module.

If a peripheral is capable of both read and write bus transfers, and setup time is specified, then the same setup time is applied to both read and write transfers. Setup time cannot be used if the slave port uses peripheral-controlled wait states.

#### Slave Write Transfers on the Avalon Bus

In the discussions of write transfers below, it is important to realize that under realistic circumstances, bus transfers are not isolated events. For example, a write transfer may immediately precede or follow an unrelated read transfer. During the write bus transfer, the target peripheral's chipselect and write\_n signals are necessarily asserted, as shown in the timing diagrams. However, after the write transfer terminates, chipselect and write\_n may remain asserted if another transfer with this slave port follows on the next bus cycle. Therefore, the timing diagrams below show unknown values on the slave port signals before and after the write transfer.

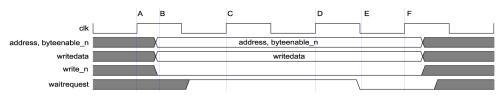

#### Fundamental Slave Write Transfer

The fundamental slave write transfer is the basis for all Avalon write transfers. All other slave write transfer modes use a super set of the fundamental signals, and implements a variation of the fundamental timing. The fundamental slave write transfer is initiated by the Avalon bus module, and transfers one unit of data from the Avalon bus module to the slave port. Fundamental slave write transfers have no latency. Example 6 shows the fundamental slave write transfer. There are zero wait states, and no setup-time or hold-time wait states. The Avalon bus module presents address, writedata, byteenable\_n, and write\_n, and then asserts chipselect. The slave port captures the address, data and control on the next rising clock edge, and the write transfer terminates immediately. The entire transfer takes only one bus cycle. The slave peripheral may then take additional clock cycles to actually process the write data after the transfer terminates. If the peripheral cannot sustain consecutive write transfers on every bus cycle, then additional design considerations are required to generate wait states.

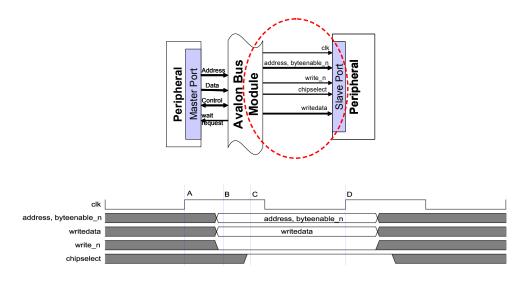

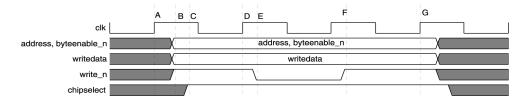

## Example 6. Fundamental Slave Write Transfer

| This Example Demonstrates                           | Relevant PTF Parameters |

|-----------------------------------------------------|-------------------------|

| A single write transfer to a synchronous peripheral |                         |

| No fixed wait state                                 | Write_Wait_States = "0" |

| No setup time                                       | Setup_Time = "0"        |

| No hold time                                        | Hold_Time = "0"         |

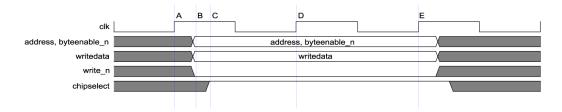

### **Example 6 Time Reference Description**

- (A) Write transfer starts on the rising edge of clk.

- (B) Registered writedata, address, byteenable\_n and write\_n signals from the Avalon bus module are valid.

- (C) Avalon bus module decodes address and asserts valid chipselect to slave.

- (D) Avalon bus module captures writedata, address, write\_n, byteenable and chipselect on the rising edge of clk, and the transfer terminates. Another read or write transfer may follow on the next bus cycle.

The fundamental write transfer is only appropriate for synchronous peripherals, which includes many on-chip peripherals, such as PIOs and timers for the Nios<sup>®</sup> processor. The timing for a fundamental write transfer is not appropriate for asynchronous peripherals, because all output signals including write\_n and chipselect are all deasserted at the same time. This would cause a race condition in, for example, an off-chip asynchronous memory. For such a memory, the Avalon bus module provides several hold time options, which are discussed in subsequent sections.

The byte enable lines byteenable\_n may be connected to the peripheral's slave port, and may be used to write a specific byte lane when writedata is wider than one byte wide. byteenable\_n is a bus with one bit for every byte lane in writedata. byteenable\_n is usually necessary for slave write transfers to off-chip, 16-bit or 32-bit memory devices that are word addressable. When writing a single byte of data, address specifies only an appropriate word or half-word address, while byteenable\_n specifies exactly which byte(s) to write. Some example cases of byteenable\_n are specified below in Table 3, assuming the slave port is a 32-bit external memory.

| Table 3. Byte Enable Usage for 32-bit Slave |                     |  |

|---------------------------------------------|---------------------|--|

| byteenable_n[3:0] Write action              |                     |  |

| 0000                                        | Write full 32-bits  |  |

| 1100                                        | Write lower 2 bytes |  |

| 0011                                        | Write upper 2 bytes |  |

| 1110                                        | Write byte 0 only   |  |

| 1011                                        | Write byte 2 only   |  |

When chipselect is deasserted, all slave port input signals should be ignored. The slave port's outputs may be driven or left undefined when the slave port is not selected. Note that the chipselect signal from the Avalon bus module may be combinatorial, and therefore may glitch, based on transitions on the address port. Furthermore, a low-to-high edge on chipselect or a high-to-low edge on write\_n cannot be used as a start write transfer trigger, because such an edge is not guaranteed to be clean. If this is not taken into consideration, the slave port will interpret erroneous write operations into unknown locations specified by an undefined address.

## Slave Write Transfer with Fixed Wait States

The ports used for a write transfer with fixed wait states are identical to those used for a fundamental write transfer. The only difference is in the timing of signals. For example, with one fixed wait state specified, the Avalon bus module waits for one additional clock cycle before deasserting the address, data and control signals. Wait states are specified by declarations made in the PTF file. They are fixed because the Avalon bus module inserts the same number of wait states for every bus transfer.

Write transfers with wait states are typically used for peripherals that cannot capture data from the Avalon bus module in a single bus cycle. In this transfer mode, the Avalon bus module presents address, writedata, byteenable\_n, write\_n and chipselect during the first bus cycle, exactly like the start of a fundamental write transfer. During the wait states, these signals are held constant. The slave port eventually captures data from the Avalon bus module within the fixed number or wait states. The transfer then terminates, and the Avalon bus module deasserts all signals at the same time. Example 7 shows an example of a slave write transfer with one wait state.