## Ryerson University Department of Electrical and Computer Engineering COE 608-Computer Organization and Architecture

| Name:                                                                       | Student Number:                                   | Sec:                                              |

|-----------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|

| Time limit: 2 hours 30 min                                                  |                                                   | Examiners: N. Mekhiel                             |

| Notes:  a) Closed book.  b) No calculators  c) Answer all questions in      | the space provided.                               | Total Marks=80, each=20 (one bonus question)      |

| Q1-1 Write MIPS Assembl                                                     | y for the following C code:-                      |                                                   |

| For(i=0; i<1000; i++) {<br>Y[i] = A*X[i] + Y[i];                            |                                                   |                                                   |

| }                                                                           | e)] is at location 1000 and address of Y[0] is at | t location 10000, register \$s0 is used for i and |

| addi \$52, \$0,<br>addi \$53, \$0,<br>addi \$53, \$0,<br>?: \$11\$54,\$0,2; | 10000; QXE0]<br>10000; QYE0]<br>HI                |                                                   |

| 90155, 52,54:                                                               | DXTID                                             |                                                   |

| ald S6, 53,54,<br>lwto, ocs51;<br>Multo, to, 51                             | XCII                                              |                                                   |

| Multo, to, 51                                                               | ; AXEC                                            |                                                   |

| lw Ti, ocs                                                                  | (); Y (i)                                         |                                                   |

| 9 18 t1, to,                                                                | Ti; axty                                          |                                                   |

| 5W T1,00                                                                    | 86) , 1717                                        |                                                   |

| addi 51,51                                                                  | 11: 141                                           |                                                   |

| 517, 57,                                                                    | 51,1000: (<160)                                   |                                                   |

| 6n2 57,                                                                     | L001)                                             |                                                   |

Q1-2 Find the performance in time for the above code if each arithmetic and logic operations takes 1 cycle, data transfer instructions takes 4 cycles, and conditional branches takes 2 cycles, unconditional branches takes 1 cycle and processor runs at 2 GHz.

3

Q1-3 Calculate the average CPI for the above code

$$CP = \frac{7x_1 + 3x_4 + 1*2}{11} = \frac{21}{11} = 2$$

Q1-4 Find performance gain of above code if MIPS uses 4 processors that could run 80% of the time in parallel.

$$T_{1} = \frac{.8 \times 10.5}{4} + \frac{.2 \times 10.5}{2} = \frac{.4 \times 10.5}{4.2}$$

| Name:  |  |

|--------|--|

| ranic. |  |

Section:

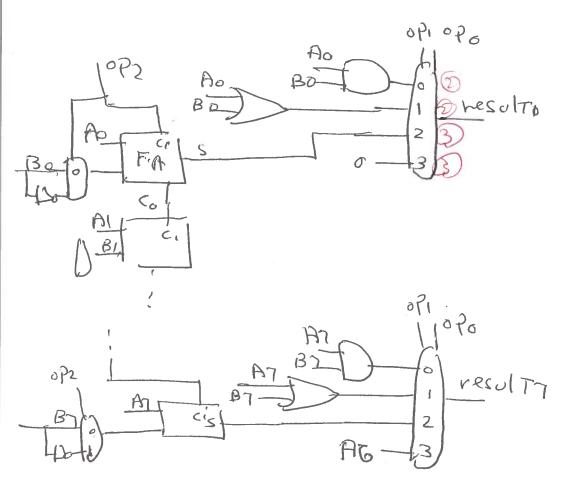

Q2-1 Design an ALU for 8 bit numbers A and B to performs operations based on the following op code:-

OP2 OP1 OP0

0 0 0 AND

0 0 1 OR

0 1 0 ADD

1 1 0 SUB

1 1 SLL (shift logic left by 1 bit of A)

| Name: |  |  |

|-------|--|--|

|       |  |  |

| 0 .1    |      |  |

|---------|------|--|

| Section | m.   |  |

| Section | /11. |  |

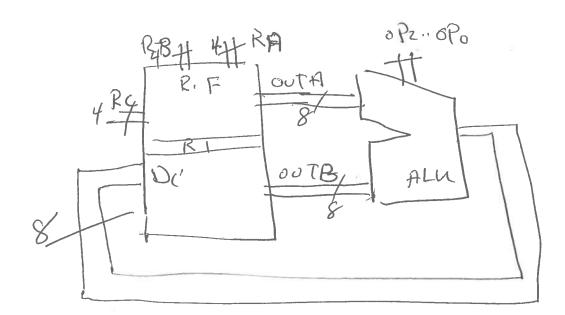

Q2-2 Assume using a register file of 16 registers each has 8 bits. It has two read ports labeld A, B and one write port labeled C. Draw a block diagram of a system that uses this register file and the above ALU to perform different operations on registers and the result is stored in one of registers (no need to draw the logic gates inside ALU or RF).

| Name: |  |

|-------|--|

|       |  |

Q2-3 List the steps using op code above and register file operations as READ, WRITE and address of each register to produce 9\*R1 and store the result in R7

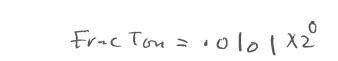

Q3-1Convert the following decimal to IEEE754 FP format:

5=1

$\frac{2}{0}$  | .3125 Number = 1.0101 x 20 0 :625 E - 127 = 0 E = 127 0 : 5 | 10111 | 171 | 01010 - - -

Section:\_\_\_\_

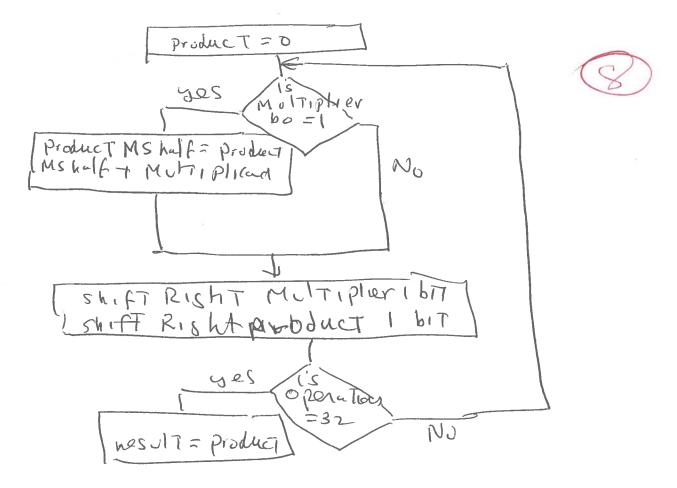

Q3-2 Draw a flow chart for algorithm to multiply two 32 bits numbers

Q3-3 Calculate how long it takes for a single multiplication operation in the above system assuming clock speed is = 2 GHz

T= 4 step \$ X 32 = 128 = 64 ns 4

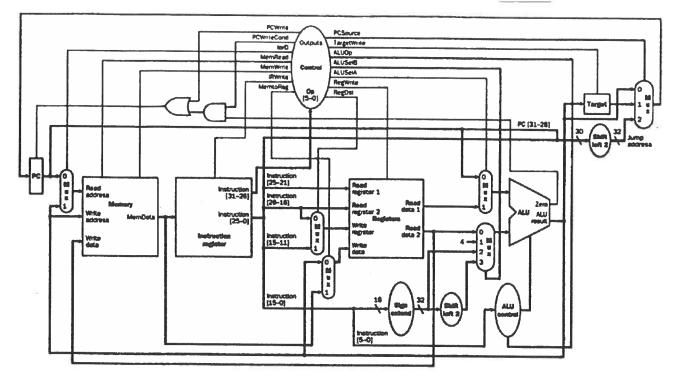

| Q4-1 For the Multicycle Data Path below, draw |                                                                                                  |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------|

|                                               |                                                                                                  |

| Folch                                         | ) IR = M(PC) JMM                                                                                 |

|                                               | ) IR=M(PC) PCTLY bey                                                                             |

| Selod                                         | 3'                                                                                               |

| lusur Culcul                                  | TEPE SS PA PC= JM SG SG SG AT PC= JM SG SG SG AT PC= JM SG S |

| (52) culculate                                | optioner for 50 50                                                                               |

| lu Sw                                         |                                                                                                  |

| 100                                           | write To                                                                                         |

| READ MONT WITH                                | Te To Munory  S D                                                                                |

| SH 50                                         | J D                                                                                              |

Q4-2 Find the value of asserted control signals in each cycle when executing the following instruction:

lw \$s8, 0(\$s4)

So! IOD=0, Men Read=1, TRW=1, ALUSTAFO, AlusuB=1, ADD, PCW-1 S1! ALUSTCA=0, ALUSTCB=3, ALUADD BTA S2! ALUSTCA=1, ALUSTCB=2, ALUADD RS+OFFSET S3! Men Ra=1 IDTD=1 S4= Men To Res=1, Resport=0, Resw=1 write To RD

| 3. T . |  |

|--------|--|

| Name:  |  |

| Sect |      |  |

|------|------|--|

| Sec  | LOTT |  |

|      |      |  |

Q4-3 Assume an application with the following frequency of use of instructions:-

lw 25%, sw 15%, arithmetic and logic 50%, conditional branch 10%

Find the performance improvement of using the multi cycle system compared to single cycle

Single cycle Tules 5 Cycles

MULTI cycle = .25x5+.15x4+.5x4+.1x3

= 1.25+.6+2+.3= 4.15 cycle

9au = 5 = 20%

6

Q5-Assume MIPS system uses pipelining with the following code:-

loop: lw \$t0, 0(\$s1) add \$t1, \$t0, \$t2 sw \$t1, 0(\$s1) addi \$s1, \$s1, 4 bne \$s1, \$s3, loop

Q5-1 Identify all the hazards in the above code

New-add on to RAW Nadd-SW on the RAW Vaddi-bne on SI RAW Mbne Central

| Name: |  |

|-------|--|

|       |  |

Section:

Q5-2 Assume using forwarding and branch delay slot, reschedule the code to improve performance

Loop! lw To, oCSI)

aldi SI, SI, 4

ald TIITOIT2

bne SI, S3, Loop

Sw TII -4 (SI)

Name:\_\_\_\_\_

Section: