# FPGA/HPS Design with Cyclone V

COE838: Lab4 & MD5 Project

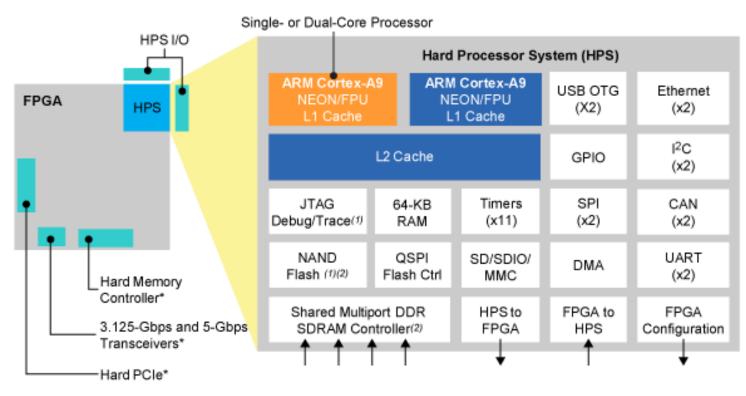

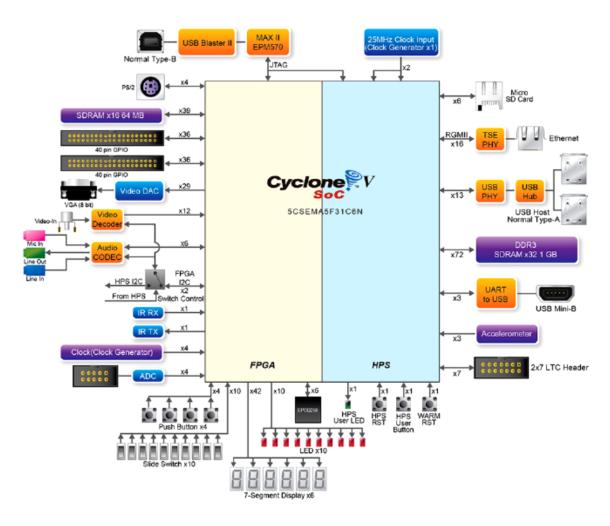

# General Overview - FPGA/HPS

\*Optional Configuration

# General Overview - FPGA/HPS

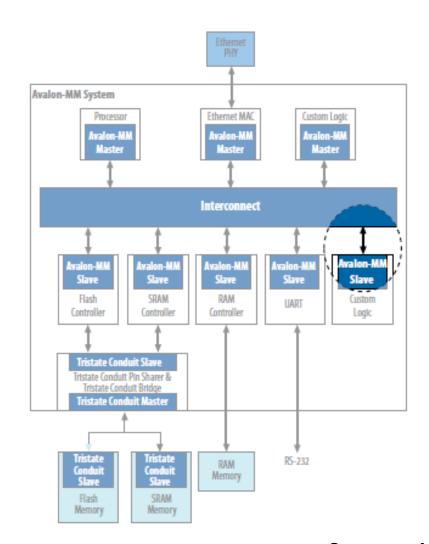

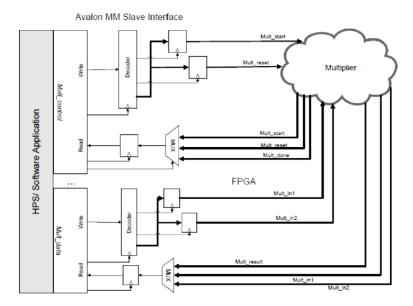

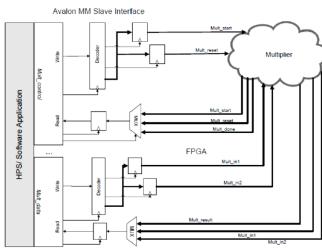

## FPGA - Avalon I/F & Interconnect

Hard vs Soft IPs

**Examples:**

**CPUs**: NIOS and ARM

**Memory Controllers**: DDR3

SDRAM, SRAM etc

I/Os: PCI, Ethernet etc

**Clock & signal generation:**

PLLs, DLLs, etc

**Arithmetic Logic**: MAC

units, multipliers etc

Table I: Common Avalon Bus Signals

| Name          | Width                | Direction | Comments                        |

|---------------|----------------------|-----------|---------------------------------|

| avs_address   | <= 64 bits           | Input     | Address of slave being accessed |

| avs_read      | 1 bit                | Input     | Read operation requested        |

| avs_write     | 1 bit                | Input     | Write operation requested       |

| avs_readdata  | 8, 16, 32 or 64 bits | Output    | Data read from slave            |

| avs_writedata | 8, 16, 32 or 64 bits | Input     | Data to be written to slave     |

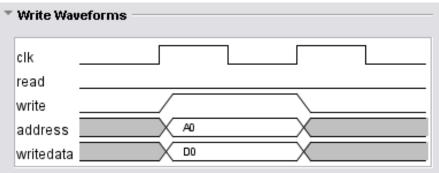

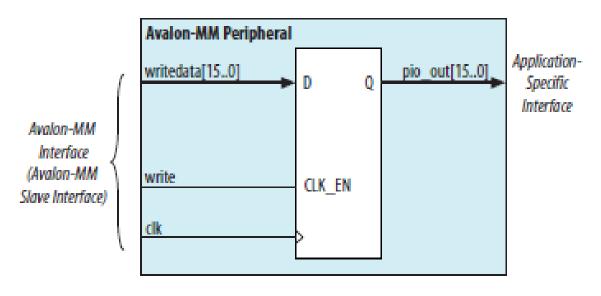

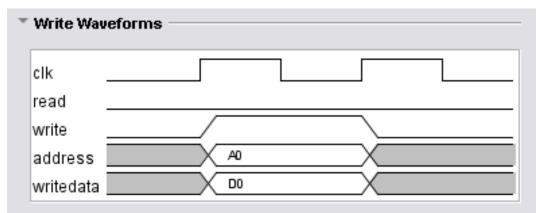

- -Most simple Avalon MM Slave example

- -The case for lab 3

```

IF(reset = '1')THEN

avs s0 readdata <= (OTHERS => '0');

entity mult data is

in1 <= (OTHERS => '0');

in2 <= (OTHERS => '0');

ELSIF(rising edge(clk))THEN

IF(avs s0 read = '1') THEN

CASE avs s0 address IS

WHEN "0000" =>

reset

mult in1

avs s0 readdata <= mult result;

WHEN "0001" =>

avs s0 readdata <= in1;

end entity mult data;

WHEN "0010" =>

avs s0 readdata <= in2;

WHEN OTHERS =>

avs s0 readdata <= (OTHERS => '0');

END CASE:

ELSIF(avs s0 write = '1') THEN

CASE avs s0 address IS

WHEN "00000" =>

in1 <= "00000000000000000" & avs s0 writedata(15 DOWNTO 0);

WHEN "0001" =>

in2 <= "00000000000000000" & avs s0 writedata(15 DOWNTO 0);

WHEN OTHERS =>

END CASE:

```

```

entity mult_data is

port (

avs_s0_address : in std_logic_vector(3 downto 0) := (others => '0'); --

avs_s0_read : in std_logic := '0'; --

avs_s0_write : in std_logic := '0'; --

avs_s0_readdata : out std_logic_vector(31 downto 0); --

avs_s0_writedata : in std_logic_vector(31 downto 0) := (others => '0'); --

clk : in std_logic := '0'; --

reset : in std_logic := '0'; --

mult_in1 : out std_logic_vector(31 downto 0); -- mu

mult_in2 : out std_logic_vector(31 downto 0); -- mu

mult_result : in std_logic_vector(31 downto 0); -- mu

);

end entity_mult_data;

```

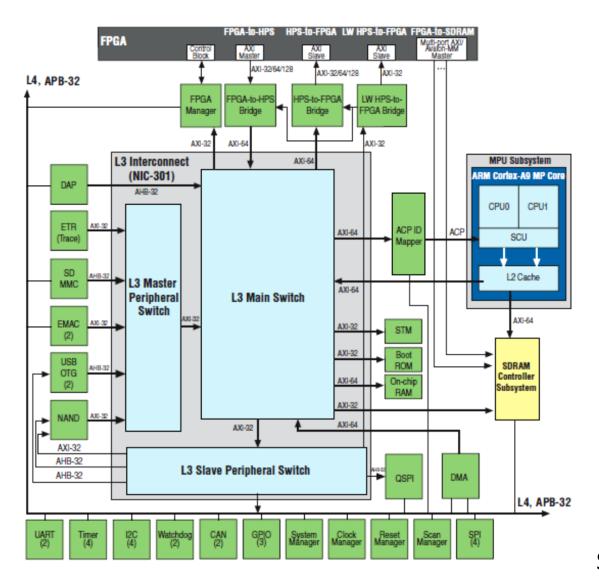

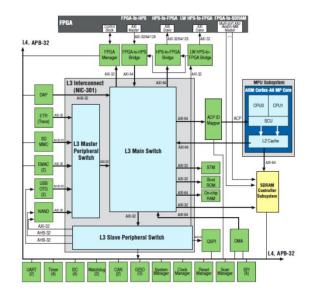

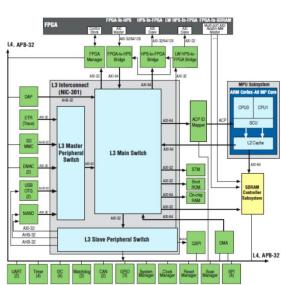

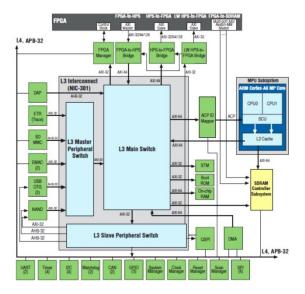

#### **HPS: ARM Cortex-A9**

#### **HPS: ARM Cortex-A9**

```

//initialize the addresses

mult_control = virtual_base + ((uint32_t) ( MULT_CONTROL_0_BASE)

mult_data = virtual_base + ((uint32_t) (MULT_DATA_0_BASE));

```

```

void copy_output() {

uint32_t word, op1, op2;

//wait for done

printf("waiting for done\n");

while(!(alt_read_word(mult_control+2) & 0x1));

printf("conversion done\n");

word = alt_read_word(mult_data+0);

op1 = alt_read_word(mult_data+1);

op2 = alt_read_word(mult_data+2);

printf("0x%08x * 0x%08x = 0x%08x. [Expected] 0x%08x\n",

if(word == (op1*op2)) {

printf("[SUCCESSFUL]\n");

success++;

}else{

```

#### **HPS: ARM Cortex-A9**

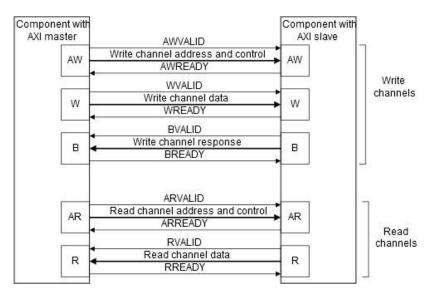

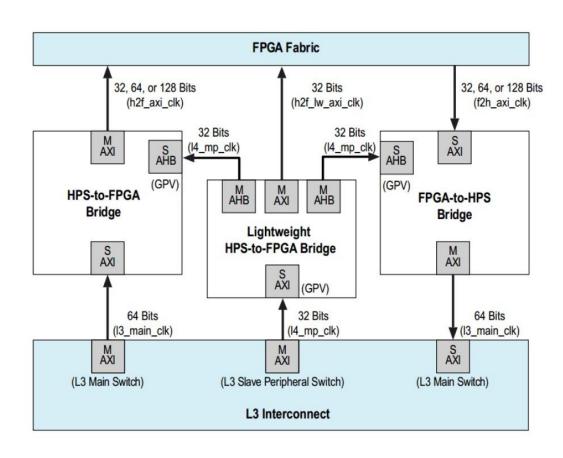

## HPS – FPGA Bridges

- -Modifies data and clock signals to support transportation (protocols, clocking etc) between components

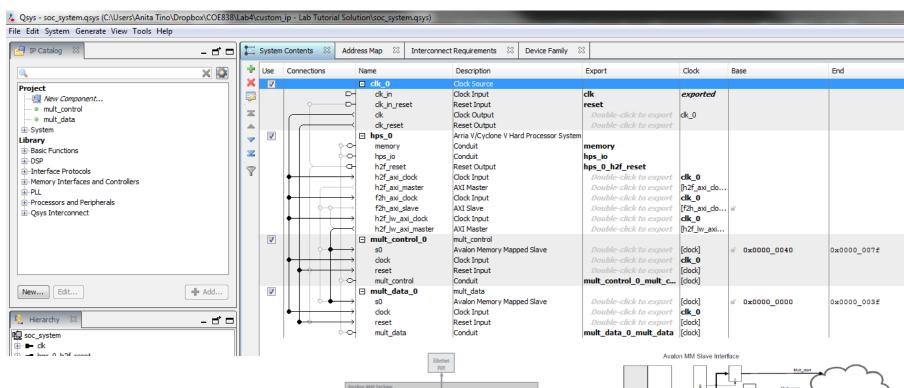

- -Qsys: Use this to design your system consisting of IPs and Avalon slaves, specify bridges connections etc.

- -Qsys will generate system interconnections, adaptation requirements between components etc

# Qsys: Putting it all together

Conduits drive signals off-chip

### Top-Level VHDL: Putting it all together

```

=> HPS ENET TX EN,

.hps io emac1 inst TX CTL

hps io hps io emac1 inst TX CTL

hps io hps io emac1 inst RX CLK

=> HPS ENET RX CLK,

.hps io emac1 inst RX CLK

hps io hps io emac1 inst RXD1

=> HPS ENET RX DATA(1),

.hps io emac1 inst RXD1

=> HPS ENET RX DATA(2),

hps io hps io emac1 inst RXD2

.hps io emac1 inst RXD2

hps io hps io emac1 inst RXD3

=> HPS ENET RX DATA(3),

.hps io emac1 inst RXD3

=> HPS SD CMD,

hps io hps io sdio inst CMD

.hps io sdio inst CMD

hps io hps io sdio inst DO

=> HPS SD DATA(0).

.hps io sdio inst DO

=> HPS SD DATA(1),

hps io hps io sdio inst D1

.hps io sdio inst D1

hps_io_hps_io sdio inst CLK

=> HPS SD CLK,

.hps io sdio inst CLK

hps_io_hps_io_sdio_inst D2

=> HPS SD DATA(2),

.hps io sdio inst D2

hps io hps io sdio inst D3

=> HPS SD DATA(3),

.hps io sdio inst D3

=> HPS USB DATA(0),

hps io hps io usb1 inst D0

.hps io usb1 inst D0

=> HPS USB DATA(1),

hps io hps io usb1 inst D1

.hps io usb1 inst D1

=> HPS USB DATA(2),

hps io hps io usb1 inst D2

.hps io usb1 inst D2

hps io hps io usb1 inst D3

=> HPS USB DATA(3),

.hps io usb1 inst D3

=> HPS USB DATA(4),

hps io hps io usb1 inst D4

.hps io usb1 inst D4

=> HPS USB DATA(5),

.hps io usb1 inst D5

hps io hps io usb1 inst D5

=> HPS USB DATA(6),

hps io hps io usb1 inst D6

.hps io usb1 inst D6

hps io hps io usb1 inst D7

=> HPS USB DATA(7),

.hps io usb1 inst D7

hps io hps io usb1 inst CLK

=> HPS USB CLKOUT,

.hps io usb1 inst CLK

=> HPS USB STP,

hps io hps io usb1 inst STP

.hps io usb1 inst STP

=> HPS USB DIR,

hps io hps io usb1 inst DIR

.hps io usb1 inst DIR

=> HPS USB NXT,

hps io hps io usb1 inst NXT

hps 0 h2f reset reset n

=> reset reset n,

mult data 0 mult data m result => mult output result, -- mult output 0 mult output.result

mult control 0 mult control m done => "000000000000000000000000" & done, --<

.done

=> in1,

-- mult input 0 mult input.in1

mult data 0 mult data m in1

mult data 0 mult data m in2

=> in2,

mult control 0 mult control m start => mult_input_start,

.start

mult control 0 mult control m reset => mult input reset

.reset

);

m0 : mult unit

PORT MAP( clk => CLOCK 50, reset => mult input reset(0), enable => mult input start(0), mult a => in1(15 DOWNTO 0), mult b => in2(15 DOWNTO 0),

mult done => done, mult result => mult output result);

END Behaviour:

```

# HPS Software: Putting it all together

```

Jooid copy_output(){

uint32_t word, op1, op2;

//wait for done

printf("waiting for done\n");

while(!(alt_read_word(mult_control+2) & 0x1));

printf("conversion done\n");

word = alt_read_word(mult_data+0);

op1 = alt_read_word(mult_data+1);

op2 = alt_read_word(mult_data+2);

printf("0x$08x * 0x$08x = 0x$08x. [Expected] 0x$08x\n", op1, op2, word, (op1*op2));

if(word == (op1*op2)) {

printf("[SUCCESSFUL]\n");

success++;

}else{

```

```

----- Iteration 27 -----

Reset done. Deasserting signal

Start successful

waiting for done

conversion done

0x0000001b * 0x0000001c = 0x000002f4. [Expected] 0x000002f4

[SUCCESSFUL]

----- Iteration 28 -----

Reset done. Deasserting signal

Start successful

waiting for done

conversion done

0x0000001c * 0x0000001d = 0x0000032c. [Expected] 0x0000032c

[SUCCESSFUL]

----- Iteration 29 -----

Reset done. Deasserting signal

Start successful

waiting for done

conversion done

0x0000001d * 0x0000001e = 0x00000366. [Expected] 0x00000366

[SUCCESSFUL]

----- Tteration 30 -----

Reset done. Deasserting signal

Start successful

waiting for done

0x0000001e * 0x0000001f = 0x000003a2. [Expected] 0x000003a2

[SUCCESSFUL]

[TEST PASSED] 30/30

```

# Project: MD5 Decryption SoC Design

## MD5 Algorithm

```

//Process the message in successive 512-bit chunks:

for each 512-bit chunk of message

//Note: All variables are unsigned 32 bit and wrar

break chunk into sixteen 32-bit words M[i], 0 ≤ i ≤ 15

var int[64] s, K

//s specifies the per-round shift amounts

//Initialize hash value for this chunk:

s[0..15] := \{ 7, 12, 17, 22, 7, 12, 17, 22,

var int A := a0 var int B := b0

s[16..31] := \{ 5, 9, 14, 20, 5, 9, 14, 20, 5,

var int C := c0     var int D := d0

s[48..63] := \{ 6, 10, 15, 21, 6, 10, 15, 21, 6,

//Main loop:

//K constants

for i from 0 to 63

K[0..3] := \{ 0xd76aa478, 0xe8c7b756, 0x242070db, \}

if 0 \le i \le 15 then

K[4..7] := \{ 0xf57c0faf, 0x4787c62a, 0xa8304613, \}

F := (B and C) or ((not B) and D)

K[8..11] := \{ 0x698098d8, 0x8b44f7af, 0xffff5bb1, \}

K[12...15] := \{ 0x6b901122, 0xfd987193, 0xa679438e, \}

else if 16 \le i \le 31

K[16..19] := \{ 0xf61e2562, 0xc040b340, 0x265e5a51, \}

K[20..23] := \{ 0xd62f105d, 0x02441453, 0xd8ale681,

F := (D and B) or ((not D) and C)

K[24..27] := \{ 0x21e1cde6, 0xc33707d6, 0xf4d50d87, \}

q := (5 \times i + 1) \mod 16

K[28..31] := \{ 0xa9e3e905, 0xfcefa3f8, 0x676f02d9, \}

else if 32 \le i \le 47

K[32..35] := \{ 0xfffa3942, 0x8771f681, 0x6d9d6122,

F := B xor C xor D

K[36..39] := { 0xa4beea44, 0x4bdecfa9, 0xf6bb4b60,

q := (3 \times i + 5) \mod 16

K[40..43] := \{ 0x289b7ec6, 0xeaa127fa, 0xd4ef3085, \}

else if 48 \le i \le 63

K[44..47] := \{ 0xd9d4d039, 0xe6db99e5, 0x1fa27cf8, \}

F := C xor (B or (not D))

K[48..51] := \{ 0xf4292244, 0x432aff97, 0xab9423a7, \}

q := (7 \times i) \mod 16

K[52...55] := \{ 0x655b59c3, 0x8f0ccc92, 0xffeff47d, \}

K[56...59] := \{ 0x6fa87e4f, 0xfe2ce6e0, 0xa3014314, \}

dTemp := D

K[60..63] := \{ 0xf7537e82, 0xbd3af235, 0x2ad7d2bb, \}

D := C

C := B

//Initialize variables:

B := B + leftrotate((A + F + K[i] + M[g]), s[i])

var int a0 := 0x67452301 //A

A := dTemp

var int b0 := 0xefcdab89 //B

var int c0 := 0x98badcfe //C

//Add this chunk's hash to result so far:

var int d0 := 0x10325476 //D

a0 := a0 + A

b0 := b0 + B

c0 := c0 + C

d0 := d0 + D

end for

var char digest[16] := a0 append b0 append c0 append d0 //(Output is in little-endian)

//leftrotate function definition

leftrotate (x, c)

return (x \ll c) binary or (x \gg (32-c));

```

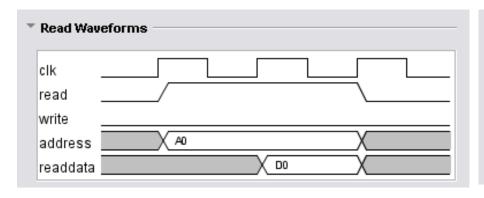

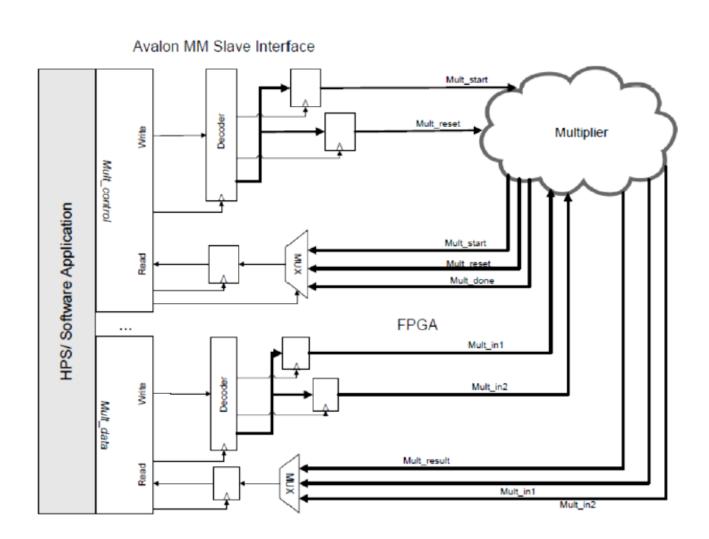

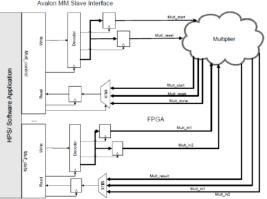

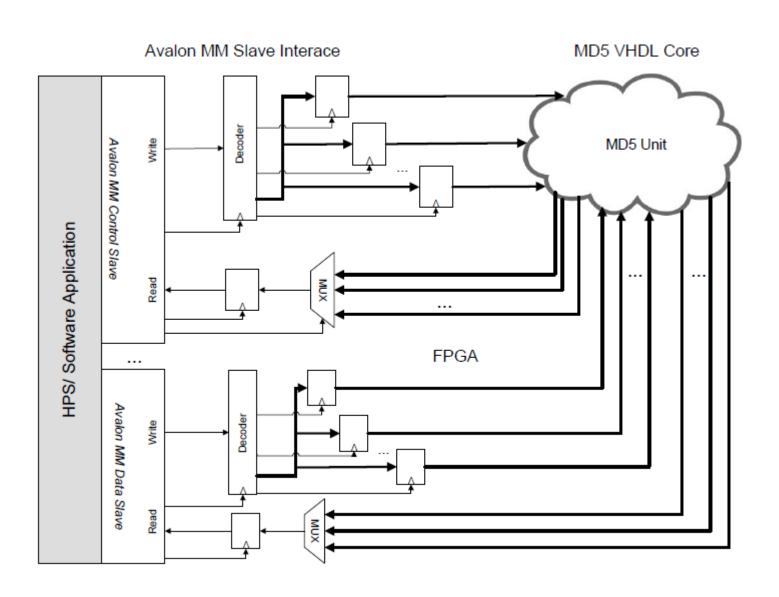

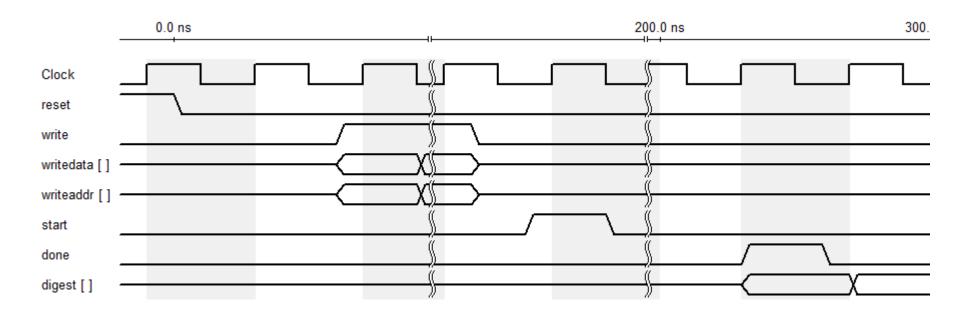

#### MD5 Avalon Slave Interface

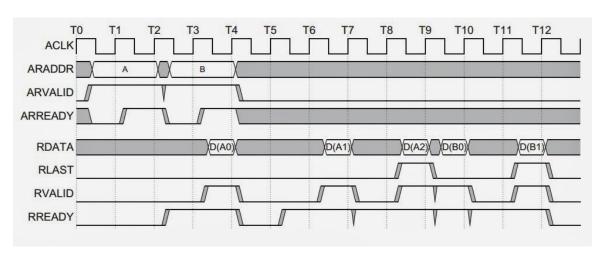

# MD5 Timing Characteristics

## MD5 Project

- Analyze the MD5 Core Obtain a thorough understanding

- VHDL RTL analysis

- Test bench => 1 core vs 32 cores

- Timing properties in ModelSim & lab manual

- Design Avalon MM Interface

- Design HPS Software Application

- Generate Messages

- Send constant data, send message

- Receive digest when complete

- Calculate hash time, # of hashes, hash rate, correct answer etc

- Parallel vs Sequential

- Formal report must follow specifications

- Bonus Pure software vs hardware